Nvis 5586A

Nvis Technologies Pvt. Ltd.

15

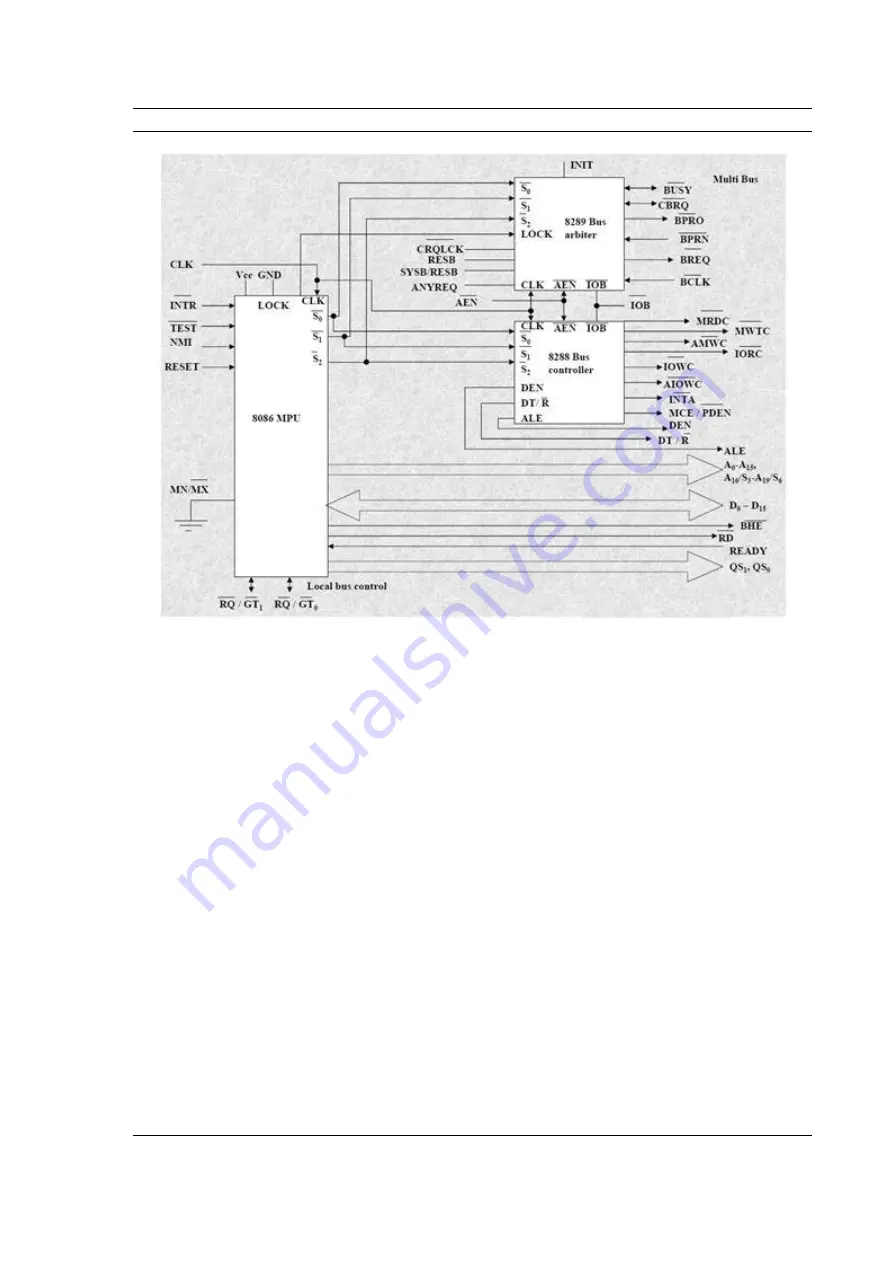

8086 Maximum Mode Block Diagram

8288 Bus Controller – Bus Command and Control Signals:

8086 does not directly

provide all the signals that are required to control the memory, I/O and interrupt interfaces.

Specially the WR*, M/IO*, DT/R*, DEN, ALE and INTA, signals are no longer produced by

the 8086. Instead it outputs three status signals S0*, S1*, S2* prior to the initiation of each

bus cycle. This 3- bit bus status code identifies which type of bus cycle is to follow.

S2*S1*S0* are input to the external bus controller device, the bus controller generates the

appropriately timed command and control signals.

The 8288 chip receive the status signal S2*, S1* and S0* and the clock from 8086. Theses

status signals are decoded to generate MRDC* (Memory read command), MWTC* (memory

write command), IORC* (I/O read command), IOWC* (I/O write command), INTA*

(Interrupt acknowledgement) signal. In addition, it can generate advanced memory and I/O

write signals AMWC* (Advanced memory write command), AIOWC* (Advanced I/O write

command) that are enabled one clock cycle earlier than the normal write control signals

because some device require wider cycle.

Summary of Contents for 5586A

Page 2: ...Nvis 5586A Nvis Technologies Pvt Ltd 2...

Page 23: ...Nvis 5586A Nvis Technologies Pvt Ltd 23 Memory Read Timing in Maximum Mode...

Page 30: ...Nvis 5586A Nvis Technologies Pvt Ltd 30...

Page 48: ...Nvis 5586A Nvis Technologies Pvt Ltd 48 Diagram of module RESET power Instruction Set Note...