Nvis 5586A

Nvis Technologies Pvt. Ltd.

16

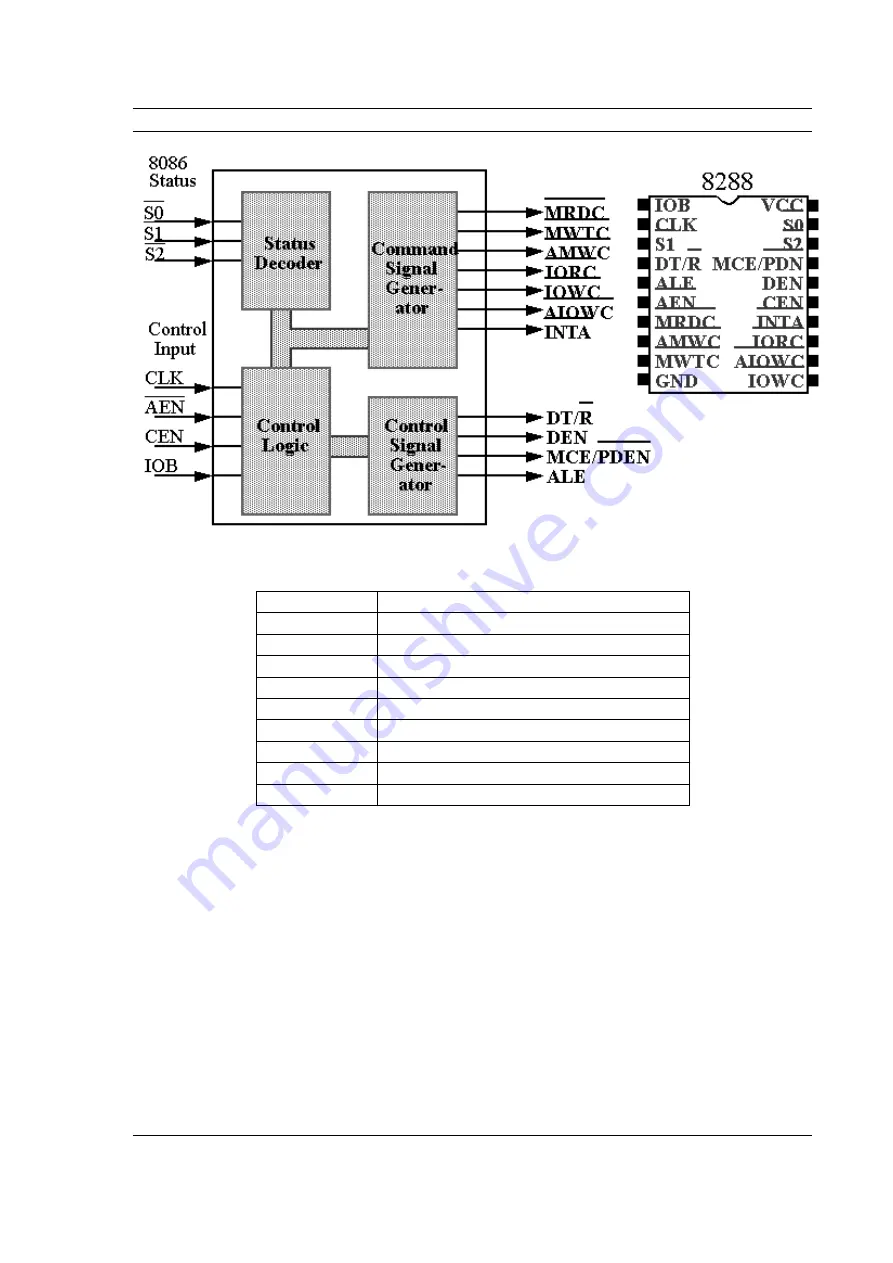

MRDC*

Memory ReaD Command

MWTC*

Memory WriTe Command

IORC*

Input/Output Read Command

IOWC*

Input/Output Write Command

INTA*

INTerrupt Acknowledge

AMWC*

Advanced Memory Write Command

AIOWC*

Advanced Input/Output Write Command

CEN

Command Enable

IOB

Input/output Bus only

MCE/PDEN*

Master Cascade/Peripheral Data Enable

The 8288 also can generate bus control signals DEN, DT/R*, ALE, MCE/ (PDEN)* i.e.

Master Cascade/Peripheral Data Enable. The function of the 1 st three signals are the same as

those in the minimum mode. The signal MCE/ (PDEN)* has 2-functions depending on the

mode in which 8288 is operating. The 8288 can either operate in I/O bus mode or system bus

mode. When CEN (command enable) and IOB (I/O bus) input pin are wired high, the 8288

operate in I/O bus mode. In this mode, the signal PDNE* functions in the same way as DEN

but it is active only during I/O instruction. This facility enables 8288 to control 2 set of

buses: System bus and I/O bus separately

With AEN* (Address enable) and CEN inputs low, the 8288 functions in system bus mode.

When multiple processors are sharing the same bus, active processors can be selected by

Summary of Contents for 5586A

Page 2: ...Nvis 5586A Nvis Technologies Pvt Ltd 2...

Page 23: ...Nvis 5586A Nvis Technologies Pvt Ltd 23 Memory Read Timing in Maximum Mode...

Page 30: ...Nvis 5586A Nvis Technologies Pvt Ltd 30...

Page 48: ...Nvis 5586A Nvis Technologies Pvt Ltd 48 Diagram of module RESET power Instruction Set Note...