Nvis 5586A

Nvis Technologies Pvt. Ltd.

17

enabling the corresponding 8288 via AEN* input. In this mode, the signal MCE (Master

cascade enable) is used for selecting the appropriate interrupt controller.

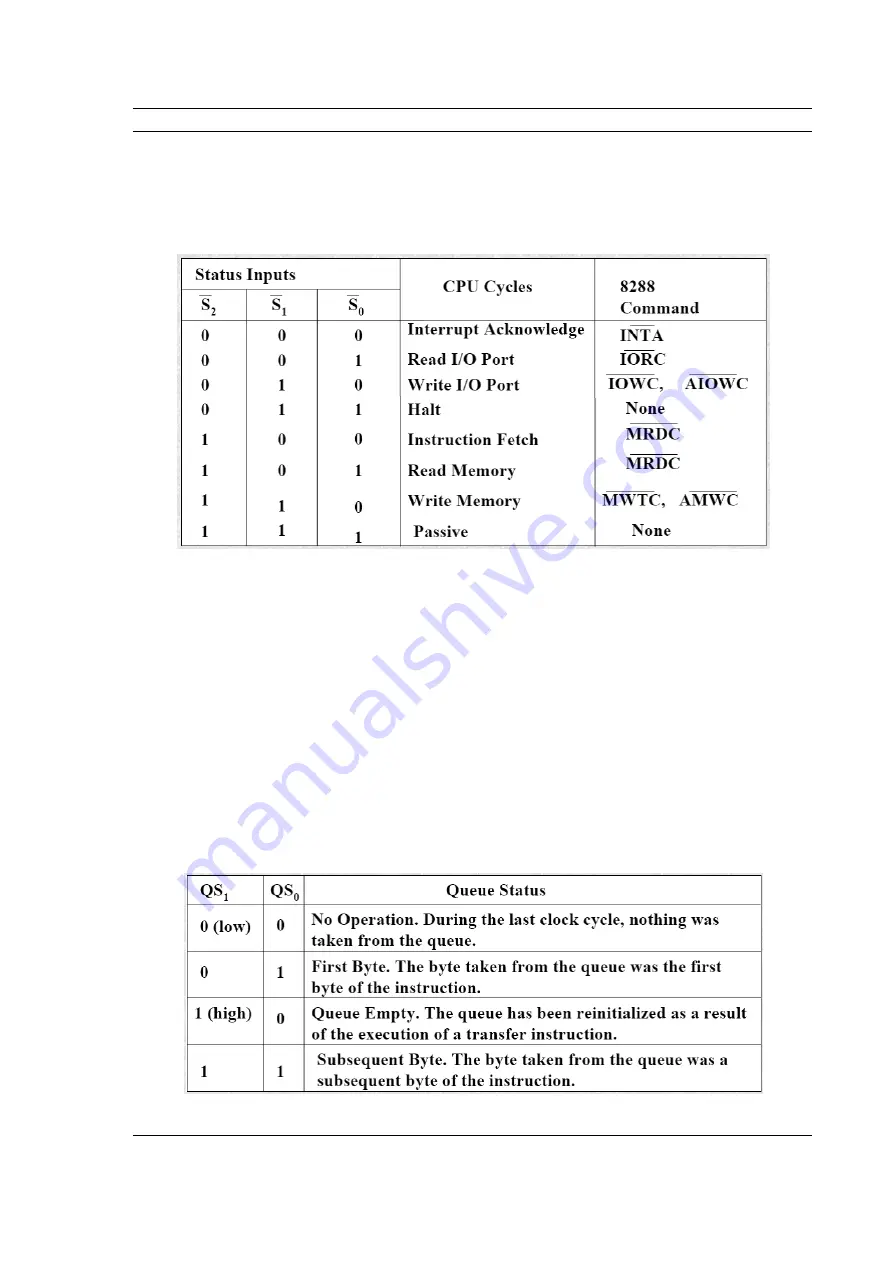

Bus Status Codes:

The 8288 produces one or two of these eight command signals for each bus cycles. For

instance, when the 8086 outputs the code S2*S1*S0* equals 001; it indicates that an

I/O

read cycle

is to be performed. In the code 111 is output by the 8086, it is signaling that no

bus activity is to take place. The control outputs produced by the 8288 are DEN, DT/R* and

ALE. These 3 signals provide the same functions as those described for the minimum system

mode. This set of bus commands and control signals is compatible with the Multibus and

industry standard for interfacing microprocessor systems.

Queue Status Signals:

Two new signals that are produced by the 8086 in the maximum-

mode system are queue status outputs QS0 and QS1. Together they form a 2-bit queue status

code, QS1QS0.

Following table shows the four different queue status.

Summary of Contents for 5586A

Page 2: ...Nvis 5586A Nvis Technologies Pvt Ltd 2...

Page 23: ...Nvis 5586A Nvis Technologies Pvt Ltd 23 Memory Read Timing in Maximum Mode...

Page 30: ...Nvis 5586A Nvis Technologies Pvt Ltd 30...

Page 48: ...Nvis 5586A Nvis Technologies Pvt Ltd 48 Diagram of module RESET power Instruction Set Note...