MSM9225B User’s Manual

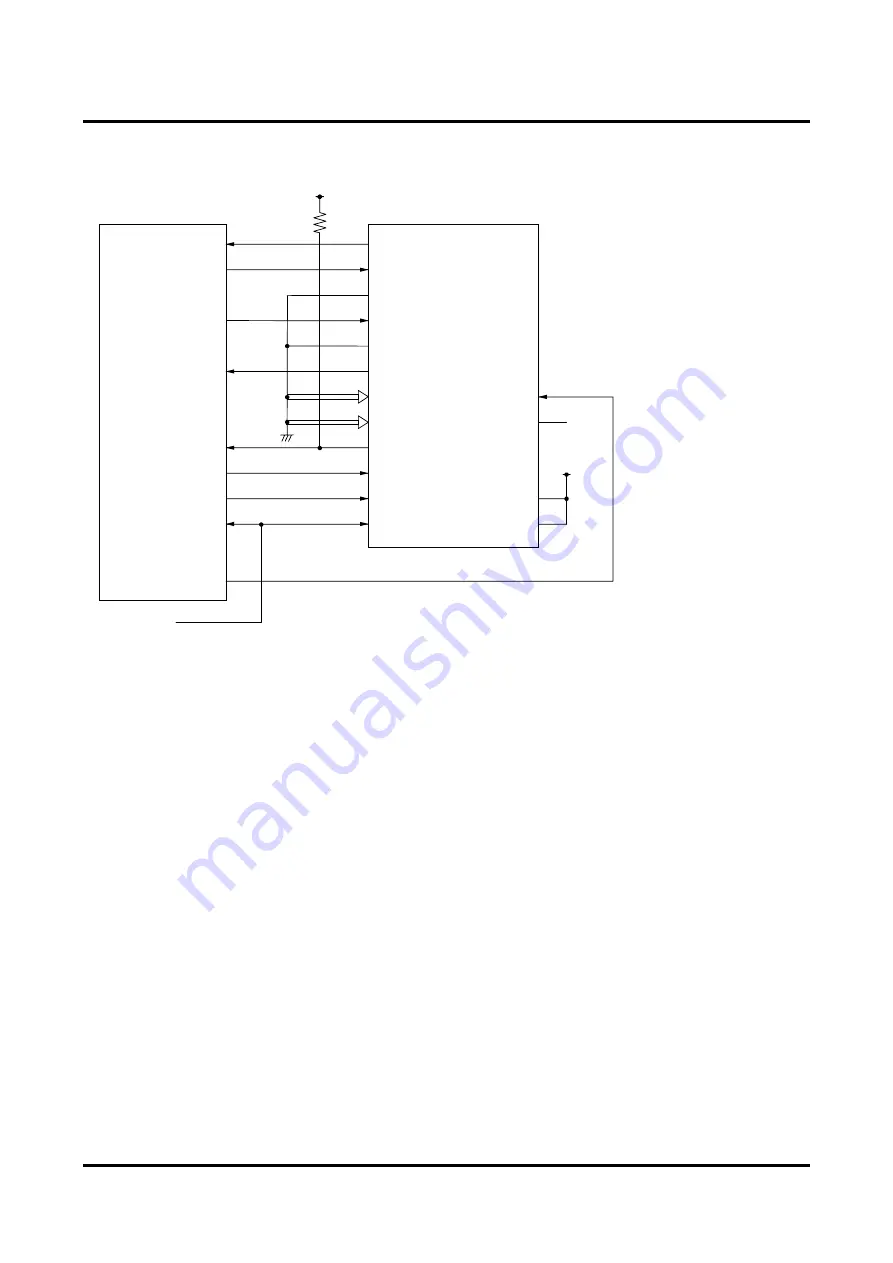

Chapter 4 Microcontroller Interface

4 – 6

4.3.1.4

Serial Interface

MSM9225B

Microcontroller

INT

CS

PALE

PRD

/SR

W

PWR

PRDY

/SWAIT

A7-0

AD7-0/D7-0

SDO

SDI

XT

XT

R/

W

WAIT

RESET

11

10

27

9

26

16

4-1, 44-41

38-31

5

7

8

25

Reset signal

13

14

30

29

10 k

Ω

+5 V

RESET

Mode0

SCLK

Mode1

SDIN

SDOUT

SCLK

Open

CLK

If the built-in oscillator circuit is

used, connect an external oscillator

in the same manner as shown in

Figure 4-2.

+5 V

INT

CS

Figure 4-5 Serial Interface

Summary of Contents for MSM9225B

Page 7: ...Chapter 1 Overview...

Page 13: ...Chapter 2 Register Descriptions...

Page 53: ...Chapter 3 Operational Description...

Page 62: ...Chapter 4 Microcontroller Interface...

Page 71: ...Chapter 5 Electrical Characteristics...

Page 81: ...Appendixes...