RECEIVER

Issue 1

Section 5

MCUK991001G8

Revision 0

– 16 –

Technical Guide

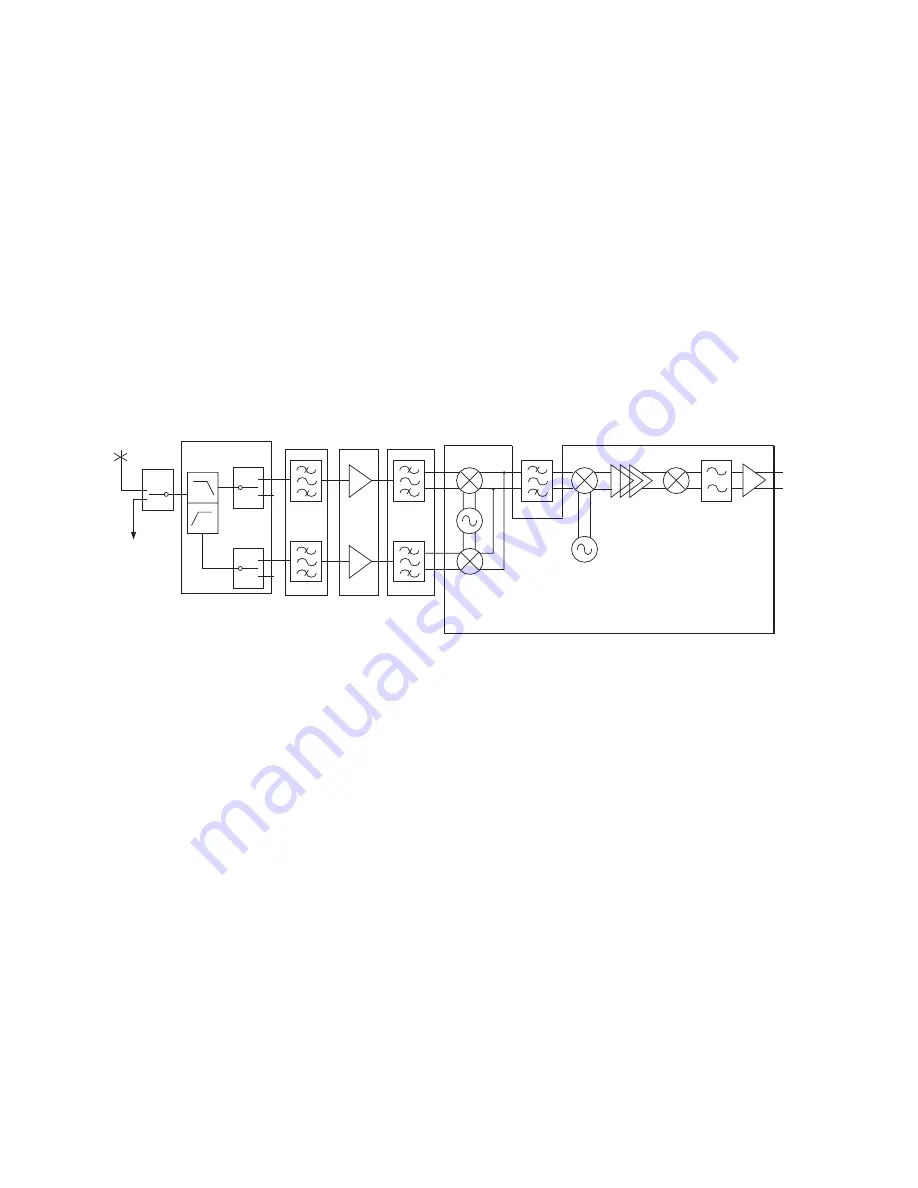

5.3 Functional Description

5.3.1 Dual Band Receiver IC

The main building block for the Dual Band Receiver is the Hitachi Bright2 IC. The receiver is a triple superheterodyne type with

the 1st IF at 225 MHz and 2nd IF at 45 MHz. The intermediate frequencies are common to both frequency bands.

The Rx IC contains the following stages:

1.

Gain controlled 1st mixer for GSM 900 band.

2.

Gain controlled 1st mixer for GSM 1800 band.

3.

Gain controlled 2nd mixer.

4.

Gain controlled IF amplifier

5.

I,Q quadrature down converter.

6.

Baseband Op Amps for further amplification and some filtering of the baseband I,Q signals.

5.3.2 Circuit Description

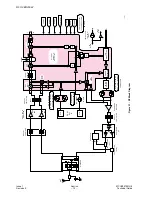

Figure 5.1: Dual Band Receiver

RF input to the receiver is either via the antenna or via the H/F RF connector. The input signal from the antenna or the H/F RF

connector is fed into the GSM 900/GSM 1800 dual band Antenna switch module which comprises a diplexer and diode

switches. The diplexer splits the two GSM frequency bands whilst the pin switches route the signal flow from the receiver and

the transmitter as required.

The output is applied to the 1st dual band receiver SAW filter which provides the roofing filter for the Rx front end for both

900 MHz and 1800 MHz bands. Note that the appropriate signal path will be set by the Antenna switch module.

The dual band LNA IC requires external matching in order to achieve a fixed gain of 17 dB (GSM 900) or 16dB (GSM 1800),

a typical noise factor of 1.7 dB on either band, and a third order intercept point at its input of -8 dBm (GSM 900) or -5 dBm

(GSM 1800).

The output from the LNA passes through a second dual band SAW filter before being matched differentially into the 1st down-

converter mixer of the Bright 2 dual band receiver IC. The gain of the 1st mixer stage can be reduced from, typically, 9 dB to

-2.5 dB (GSM 900) or 8.5 dB to -3.5 dB (GSM 1800); this is required for operation under strong signal conditions where input

power levels are greater than -40 dBm.

The mixer has a minimum third order input intercept point of 2 dBm (GSM 900) or -0.5 dB (GSM 1800) with a maximum SSB

noise figure of 12 dBm (GSM 900) or 10.6 dB (GSM 1800). The 1st local oscillator output is generated by a PLL employing a

dual modular RF VCO. The output from the VCO is split and fed directly to the Bright 2, which then buffers the signal and

differentially splits this to both 900 MHz and 1800 MHz mixers. The frequency range of the local oscillator for GSM 900 is 1160-

1185 MHz, and for GSM 1800 is 1580-1655 MHz.

The IF output at 225 MHz from the 1st mixer is filtered by the differential IF SAW filter before it is fed into the 2nd mixer and

down-converted to the 2nd IF of 45 MHz. The output is then fed to the gain-controlled IF amplifiers

The output from the IF amplifiers is fed into two quadrature mixers where it is converted down to baseband. The IF LO is

generated at 540 MHz by an external discrete VCO module. An on-chip divider on the Rx IC divides this by twelve. It also

produces two outputs in quadrature to generate the baseband I and Q signals. The outputs from the mixers are connected to

external pins via dual differential low pass filters and a pair of buffer amplifiers.

DUAL BAND

LNA

PGC

1800

DUAL BAND

RX SAW

DUAL BAND RECEIVER

(PART)

IF

SAW

1st

Mixer

2nd

Mixer

900

1800

900

LPF

Rx

Tx

Rx

Tx

Ext

Ant.

HPF

10154-1

DUAL BAND

Rx SAW

S701

I

Q

Demodulator

U701

S700

FL702

U700

FL703

DIPLEXER

FL700