S

D

D

0

0

0

2

6

A

E

M

MN

6

6

2

7

8

5

T

B

U

C

B

.

S

u

b

c

o

d

e

d

a

t

a

r

e

a

d

B

y

i

n

p

u

t

t

i

n

g

a

c

l

o

c

k

f

r

o

m

S

B

C

K

p

i

n

,

s

u

b

c

o

d

e

d

a

t

a

,

P

t

o

W

,

c

a

n

b

e

r

e

a

d

f

r

o

m

S

U

B

C

p

i

n

.

T

h

e

t

i

m

i

n

g

i

s

s

h

o

w

n

i

n

t

h

e

f

i

g

u

r

e

b

e

l

o

w

.

S

i

n

c

e

s

u

b

c

o

d

e

d

a

t

a

v

a

r

i

e

s

e

v

e

r

y

f

a

l

l

i

n

g

e

d

g

e

o

f

N

C

L

D

C

K

,

i

n

p

u

t

8

c

l

o

c

k

s

o

f

S

B

C

K

e

v

e

r

y

f

a

l

l

i

n

g

e

d

g

e

o

f

N

C

L

D

C

K

,

a

n

d

s

w

i

t

c

h

t

h

e

c

o

n

t

e

n

t

o

f

S

U

B

C

o

u

t

p

u

t

t

o

P

t

o

W

.

T

h

e

n

S

U

B

C

o

u

t

p

u

t

w

h

i

c

h

v

a

r

i

e

s

i

n

s

y

n

c

h

r

o

n

i

z

a

t

i

o

n

w

i

t

h

t

h

e

f

a

l

l

i

n

g

e

d

g

e

o

f

S

B

C

K

i

s

r

e

c

e

i

v

e

d

a

t

t

h

e

t

i

m

i

n

g

o

f

t

h

e

r

i

s

i

n

g

e

d

g

e

o

f

S

B

C

K

.

A

l

l

s

u

b

c

o

d

e

d

a

t

a

c

a

n

b

e

r

e

a

d

b

y

r

e

p

e

a

t

i

n

g

t

h

e

o

p

e

r

a

t

i

o

n

a

b

o

v

e

f

o

r

e

a

c

h

N

C

L

D

C

K

.

B

y

i

n

p

u

t

t

i

n

g

S

B

C

K

,

t

h

e

c

o

n

t

e

n

t

o

f

F

L

A

G

o

u

t

p

u

t

w

i

l

l

v

a

r

y

.

S

o

m

e

a

s

u

r

i

n

g

t

h

e

e

r

r

o

r

r

a

t

e

w

h

i

l

e

r

e

a

d

i

n

g

s

u

b

c

o

d

e

i

s

n

o

t

p

o

s

s

i

b

l

e

.

T

a

k

e

i

t

i

n

t

o

c

o

n

s

i

d

e

r

a

t

i

o

n

w

h

e

n

d

e

s

i

g

n

i

n

g

t

h

e

s

y

s

t

e

m

.

T

y

p

.

T

y

p

.

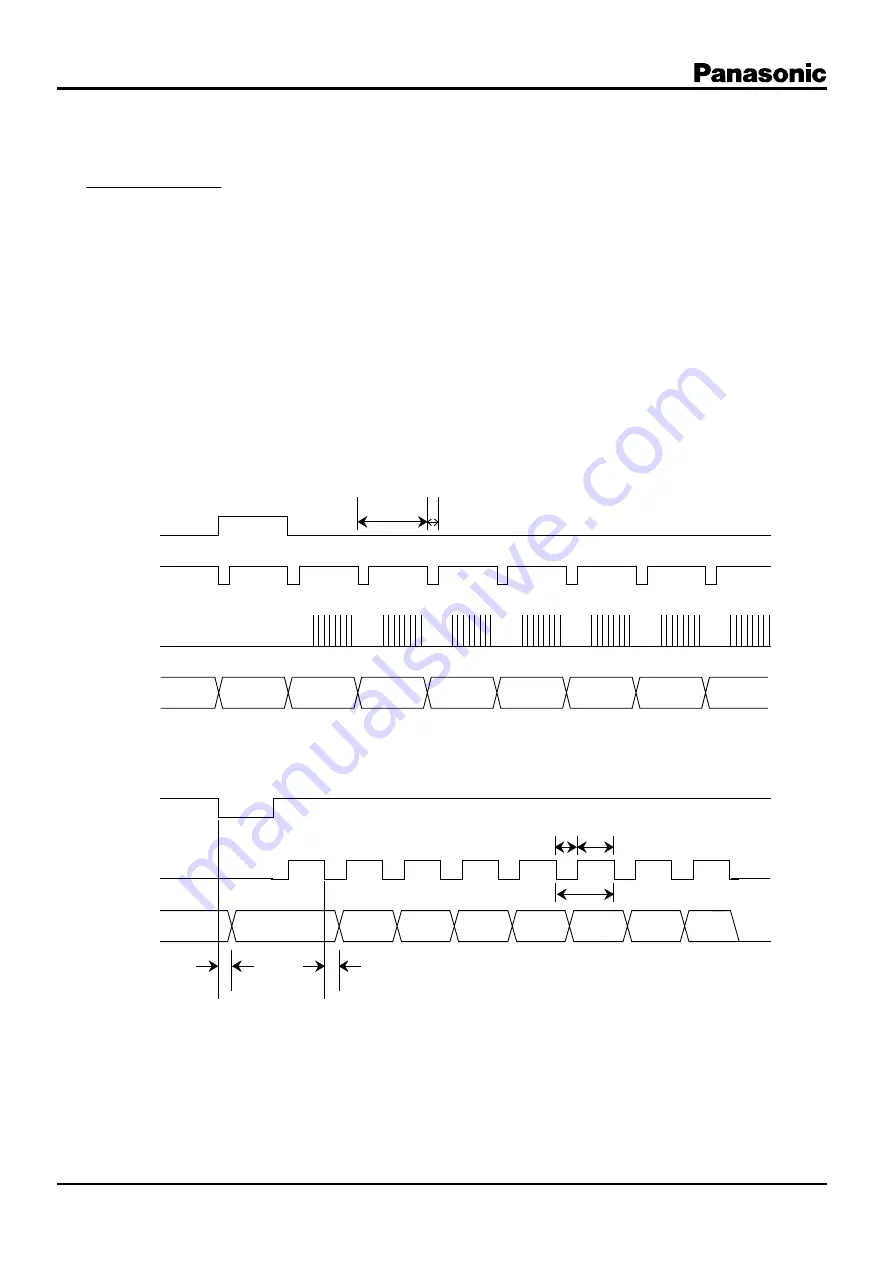

1

3

6

µ

s

1

.

6

µ

s

B

L

K

C

K

SBCK

S

U

B

C

S

0

S

1

P

1

t

o

W

1

P

2

t

o

W

2

P

3

t

o

W

3

P

4

t

o

W

4

P

5

t

o

W

5

P

6

t

o

W

6

P

7

t

o

W

7

NCLDCK

S

B

C

K

N

C

L

D

C

K

S

U

B

C

P

Q

R

S

T

U

V

W

F

i

g

u

r

e

7

-

2

-

2

N

C

L

D

C

K

,

S

U

B

C

,

a

n

d

S

B

C

K

t

i

m

i

n

g

c

h

a

r

t

*

*

*

*

*

*

:

R

e

f

e

r

t

o

t

h

e

v

a

l

u

e

s

s

p

e

c

i

f

i

e

d

i

n

t

h

e

P

R

O

D

U

C

T

S

T

A

N

D

A

R

D

S

.

6

2

Maintenance/

Discontinued

Maintenance/Discontinued includes following four Product lifecycle stage.

(planed maintenance type, maintenance type, planed discontinued typed, discontinued type)