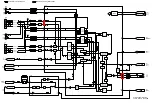

8.7.

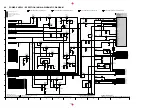

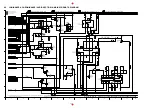

TBC/DNR PACK SCHEMATIC DIAGRAM

L

39P

C3371

100

R3364

30P

C3372

39u

L3312

68

R3363

(PB:ON)

DTC363EK

QR3301

EE

100

R3365

B1

A3

A5

A4

C3315 0.01

VIDEO MAIN SIGNAL PATH PLAYBACK MODE

VIDEO MAIN SIGNAL PATH IN REC MODE

1.7

0.8

1.2

2.7

2.9

3.4

3.4

3.4

0

2.5

2.5

2.5

3.3

2.4

0.1

0

2.5

0

0

3.4

0

3.4

3.4

3.4

0

3.4

0

3.4

0

2.5

0

0

2.5

3.5

0

1.5

2.5

1.3

2.5

0.9

0.8

1.2

1.5

1.7

2.5

1.7

1.2

C3318 0.01

2.5

0.8

0.8

2.5

1.1

1.1

3.4

3.4

2.1

1.3

2.5

3.4

3.4

1.5

2.1

2.1

1.5

11.1

11.1

4.1

11.8

2.1

2.7

5.9

5.3

11.8

1.7

1.1

5.1

1.7

3.4

2.3

3.4

2.8

5.1

2.8

2.2

5.1

1.5

2.1

2.8

11.8

1.6

11.1

2.2

VRTY AD

BIAS AD

CLAMP P

VSS IO3

SDA

SCK

VDD IO3

IIC SEL

RESET

D VSS3

MODE 2

MODE 3

D VDD3

TIN 14

TIN 13

TIN 12

TIN 11

TIN 10

VSS RAM3

TIN 9

TIN 8

VDD RAM3

TIN 7

TIN 6

TIN 5

TIN 4

T IN3

TIN 2

TIN 1

VSS RAM2

VDD RAM2

TBC WE

HSW IN

PV IN

ADV OUT

D VSS2

OSD CK

D VDD2

TEST 3

TEST 2

TEST 1

VSS IO2

HD OUT

VD OUT

VDD IO2

OSD A2

OSD A1

OSD B

OSD G

OSD R

SYNC DET

NONST

F50

VSS IO1

PAL ID

MASKP 2

VDD IO1

MASKP 1

VSS RAM1

TOUT 4

TOUT 3

VDD RAM1

TOUT 2

TOUT 1

DT CLK

D VSS1

DTMB

TIN 15

D VDD1

TIN 16

KILLER

DOC IN

CSYNC IN

MODE 1

VSS VCO

FIL 2

FIL 1

VDD VCO

FSC IN

VSS PLL

VDD PLL

A VSS2

VREF DA

BIAS DA1

BIAS DA2

Y OUT

VSS YCDA

C OUT

VDD YCDA

A VSS1

VRT CAD

VSS CAD

C IN

VDD CAD

VRB CAD

VRB YAD

VDD YAD

Y IN

VSS YAD

YC IN

PB

REC

PB

REC

CONTROL

TIMING

SYNC

MEMORY

SEP.

Y/C

3D

ADJ.

DELAY

4FSC

A/D

PB

REC

CLAMP

PED.

TBC

DNR

3D

LNR

YNR

CHANGE)

(SYNC

EXPANSION

BLACK

CNR

EQ

YNC

EQ

ADJ.

DELAY

(BURST CHANGE)

ENCODER

SAMPLING

UP

SAMPLING

UP

+

8FSC

D/A

8FSC

D/A

DECODER

4FSC

A/D

BIAS

3D NR TBC)

(3D Y/C SEP.&

TC90A88F

IC3301

0.1

C3311

0.1

C3309

33u

L3313

B3

1500P

C3308

4700

R3318

B8

0

R3303

B9

0.1

C3305

0.1

C3306

0.1

C3307

0.1

C3301

0.1

C3302

0.1

C3303

15K

R3301

10K

R3308

VLP0157

LB3301

VLP0157

LB3311

33K

R3302

8200P

C3330

(RESET)

R3112N251A

IC3302

CD

GND

VDD

4

5

OUT

1

2

3

10K

R3307

6V47

C3353

VLP0157

LB3307

16V10

C3350

(2.5V REG.)

PQ1K253M2ZP

IC3303

0.01

C3351

NR

GND

VOUT

VC

GND

VIN

4

5

6

3

2

1

0.1

C3329

0.1

C3328

0.1

C3331

0

R3306

VLP0157

LB3310

VLP0157

LB3309

A1

A2

6V47

C3332

VLP0157

LB3306

VLP0157

LB3308

0.01

C3327

0.01

C3326

VLP0157

LB3305

6V47

C3310

VLP0157

LB3304

6V47

C3323

VLP0157

LB3303

6V47

C3321

22K

R3305

1

C3324

1

C3325

0.1

C3322

C3317 0.01

C3312 0.01

C3313 0.01

C3314 0.01

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0.1

C3319

0.1

C3320

A5

200

R3315

2SB1218A

Q3315

(AMP)

4700

R3340

2SD1819A

Q3301

(AMP)

330

R3309

2SB1218A

Q3304

(INV.)

620

R3316

1K

R3310

27u

L3301

3P

C3354

12P

C3333

8P

C3334

1K

R3311

2SB1218A

Q3302

(AMP)

B7

B6

B5

B4

(B)

2200

R3314

(AMP)

2SD1819A

Q3303

1500

R3313

2K

R3312

(AMP)

2SD1819A

Q3307

820

R3319

1K

R3320

22u

L3305

12P

C3338

27P

C3340

(B)

820

R3325

220

R3317

(AMP)

2SD1819A

Q3308

1K

R3323

470

R3324

0.01

C3355

0.1

C3362

1800

R3321

2200

R3339

1K

R3322

2SD1819A

Q3310

(AMP)

22u

L3308

2SB1218A

Q3312

(AMP)

4700

R3330

16V47

C3337

0.1

C3352

910

R3331

12P

C3345

12P

C3347

27u

L3307

8P

C3346

1K

R3332

620

R3333

2SB1218A

Q3313

(INV.)

2SD1819A

Q3314

(AMP)

680

R3334

560

R3335

(AMP)

2SD1819A

Q3311

1K

R3326

0.01

C3316

1200

R3328

12P

C3342

12P

C3344

0.1

C3341

27u

L3306

8P

C3343

750

R3329

1200

R3327

6V47

C3348

0.1

C3349

22u

L3304

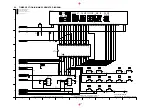

6

5

4

3

2

1

REG 12V

VV Y OUT

GND (DNR)

VV C OUT

GND (DNR)

AUDIO SECTION PP3002(F-23)

TO LUMINANCE & CHROMINANCE/

PS3301

B3

A3

B1

A4

A1

A2

MAIN IIC CLOCK

MAIN IIC DATA

DIGITAL 5V

FSC

REG 3.3V

GND (DNR)

SEP Y OUT

GND (DNR)

SEP C OUT

GND (DNR)

SEP IN

GND (DNR)

HEAD SW

ADV

Y/C C OUT

TBC MODE 0

AUDIO SECTION PP3001(E-23)

TO LUMINANCE & CHROMINANCE/

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

PS3302

WITH PAL COLOUR SIGNAL.(SP MODE)

THE MEASUREMENT MODE OF THE DC VOLTAGE OUT OF THE BRACKETS ON THIS DIAGRAM IS PLAYBACK MODE

WITH PAL COLOUR SIGNAL.(SP MODE)

NOTE:THE MEASUREMENT MODE OF THE DC VOLTAGE IN THE BRACKETS( )ON THIS DIAGRAM IS RECORD MODE

11

10

9

8

7

6

5

4

3

2

1

G

F

E

D

C

B

A

NV-HS880EG/B/EC/EE

TBC/DNR PACK SCHEMATIC DIAGRAM

45

Summary of Contents for NV-HS880EG

Page 16: ...4 REMOVAL OF THE MAIN C B A Remove Screw F Remove 4 Screws G Unlock 2 Tabs H Fig D5 16 ...

Page 23: ...3 3 8 CIRCUIT BOARD LAYOUT 23 ...

Page 26: ...10 2 CASING PARTS SECTION 26 ...

Page 27: ...10 3 PACKING PARTS SECTION 27 ...

Page 28: ...11 REPLACEMENT PARTS LIST 11 1 CHASSIS PARTS SECTION PARTS LIST 28 ...

Page 41: ...D7501 MAZ4220NMF DIODE MAVD 41 ...

Page 43: ...K7301 ERJ6GEY0R00V M RESISTOR CH 1 10W 0 D0GBR00JA017 43 ...

Page 46: ...Q1104 2SD1992A R TRANSISTOR 46 ...

Page 48: ...R0715 ERJ3GEYJ223 M RESISTOR CH 1 16W 22K 48 ...