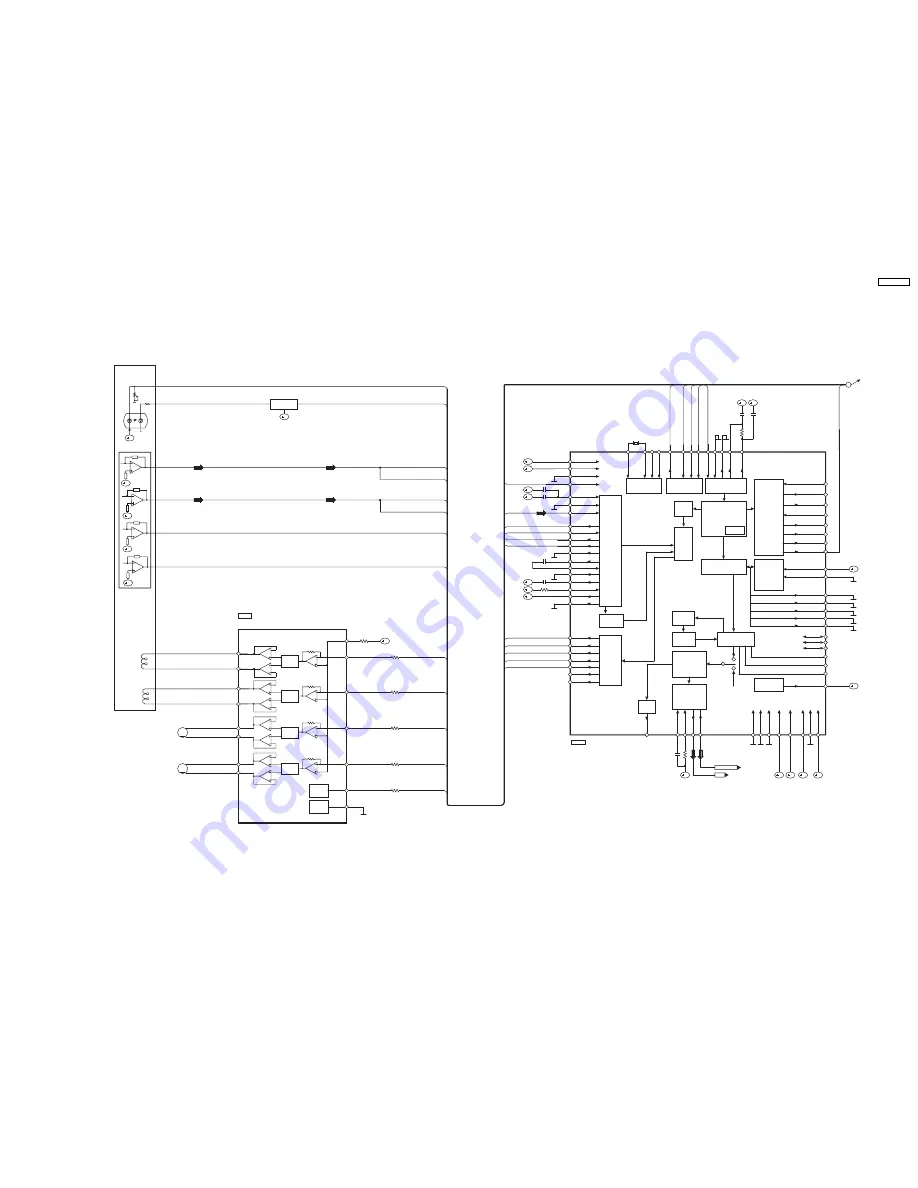

16 Block Diagram

CD SIGNAL

RCH

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

B

M7302

SPINDLE

MOTOR

M7301

TRAVERSE

MOTOR

M

M

T-

T+

F+

F-

PHOTO DETECTOR

OPTICAL PICKUP

SEMICONDUCTOR

LASER

Q7601

LASER

POWER DRIVE

FOCUS COIL

TRACKING

COIL

B

B

B

B

E

F

B

A

LPD

LD

C

D

B

A

B

F

E

MN6627954MA

SERVO PROCESSOR/

DIGITAL SIGNAL

PROCESSOR/

DIGITAL FILTER

D/A CONVERTER

IC7001

A, B, C, D, E, F

TO MAIN BLOCK

A

X7201

IC7002

BA5948FPE2

IN4

27

TRP

IN3

28

FOP

IN2

1

TRVP

IN1

3

SPOUT

PC2

2

VREF

26

D4-

18

D4+

17

D3-

16

D3+

15

D2+

14

D2-

13

D1+

12

D1-

11

PC1

4

PC

MUTE

[CH1]

LEVEL

SHIFT

LEVEL

SHIFT

LEVEL

SHIFT

LEVEL

SHIFT

[CH3]

[CH4]

[CH2]

[CH1]

MUTE

[CH2]

4 CH DRIVE

TRV+

TRV-

SP-

SP+

79

81

80

70

69

67 68

51 53 52

54

55

82

61

72

47

35~40

31

42

41

49

48

45

43

33

32

34

44

22

21

24

25

23

29

30

66

57

AVSS1

TX

SRVMON1

SRVMON0

NTEST

NRST

AVDD2

AVSS2

ARFFB

ARFF

LD

/RST

LPD

ARFF

PC

SPOUT

TRVP

TRP

FOP

ARFOUT

ARFDC

RFOUT

RFIN

CENV

CTRCRS

OSCIN

VREF

RFENV

PC

SPOUT

TRVP

TRP

FOP

LD

PD

A,B,C,D,E,F

NSRVMONON

NTEST2

MDATA

ARFIN

ARFF

BLKCK

IREF

DSLF

PLLF

PLLFO

TXTCK

(SBCK)

PRAMVDD33

PRAMVSS33

D0~D15

A0~A11

BA0,BA1

TXTD

DQSY

(SUBC)

(TXNCLDCK)

BLKCK

FLAG

65

71

20

18

83~92,94~99

1~7,11~15

16,17

NWE,NCAS

8,9

63

64

62

NRAS,SDRCK

(LRCK)

(BCLK)

(SRDATA)

EXT0

EXT2

EXT1

10,100

(DVDD2)

76

MCLK

MLD

STAT

(PMCK)

(SMCK)

X2

X1

AVDD1

OUTR

OUTL

58

IOVDD1

77

IOVDD2

27

DRVDD

93

DVDD1

28

DVDD2

76

DVSS1

26

DVSS2

78

DVSS3

60

59 56

46

50

CMOS

RF

AMPLIFIER

TIMING

GENERATOR

[GEN]

SUBCODE

INTERFACE

[DEMECC]

1Mbit

DRAM

REGULATOR

EFM DEMODUALTION

SYNC INTERPOLATION

CIRC ECC

CDROM ECC

[DEMECC]

MICRO COMPUTER

INTERFACE

[MCIF]

DSL/PLL/VCO

[DSLPLL]

SPINDLE

CPU

[DSV]

SERVO

CPU

[DSV]

CIRC RAM

BUS CONTROL UNIT

[BCU]

MP3/WMA

DECORDER

FS

CONVERTER

[FSC]

SERIAL OUTPUT

INTERFACE

[DAO]

DIGITAL FILTER

1bitDAC

PWM LOGIC

[DF, MASH]

ANALOG

LOWPASS

FILTER

DIGITAL

OUT

OUTPUT

PORT

A/D

CONVERTER

MLD

MCLK

MDATA

STAT

SA-AK340EE

53