58

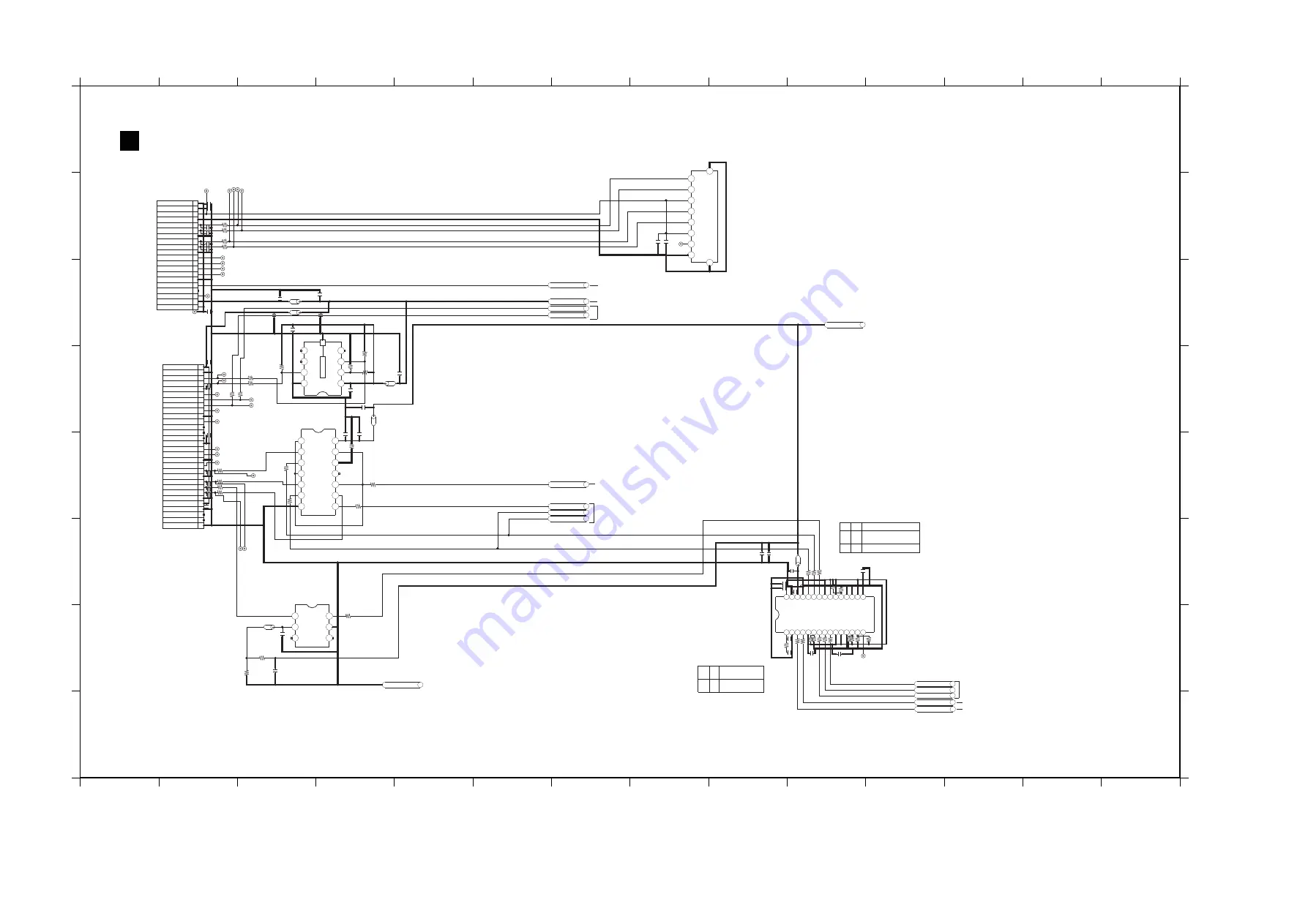

12.7. MAIN (ALLPLAY/LAN) CIRCUIT

A

1

2

3

4

5

6

7

8

9

10

11

1

2

13

14

1

2

3

4

5

6

7

8

9

10

11

1

2

13

14

C

D

B

E

G

H

F

A

C

D

B

E

G

H

F

A

SA

-PMX150EG/PC,

SA

-PMX15

2

EG

M

A

IN (

A

LLPL

AY

/L

A

N) CIRCUIT

M

A

IN (

A

LLPL

AY

/L

A

N) CIRCUIT

S

CHEM

A

TIC DI

A

GR

A

M -

6

CLK_RETRANS_BCLK

CLK_RETRANS_SDO

CLK_RETRANS_LRCK

ALL_ASYNC_RESET

ALL_ASRC_MUTE

*

C9027

16V

CK9026

R9032

*

*

R9037

R9033

*

R9036

*

*

C9026

16V

*

R9038

*

R9030

R9013

*

ALL_UART_TX

PW_3R3V_ALL

PW_3R3V_ALL

*

LB9004

*

LB9001

C9036

F1G1C104A146

16V

ALL_UART_RX

C9030

*

50V

C9031

*

50V

10

7

3

42

65

8

9

1

*

CN9002

CK8116

G_MR_RESET

R9034

*

C9040

F1H1H104B047

50V

F1G1C104A146

C9037

16V

CLK_ALL_BCLK

CLK_ALL_SDOUT

ALL_SEL

ALL_SEL

CLK_ALL_LRCK

CK9007

CK9006

CK9003

C9042

50V

*

C9006

50V

C9007

*

50V

*

C9016

16V

R9009

*

CK9005

CK9004

CK9025

CK9024

*

C9011

16V

6

7

5

9

14

11

10

13

12

17

18

15

16

8

1

3

4

2

20

19

*

CN9001

*

C9009

50V

C9034

F1H0J1060006

6.3V

*

C9010

6.3V

*

C9018

16V

*

LB9000

CK9008

CK9010

CK9011

CK9009

PW_3R3V_ALLPLAY

*

R9008

C9008

*

50V

R9006

*

*

R9007

F1G1C104A146

C9038

16V

C9041

F1H1H104B047

50V

ETHERNET_RX-

ETHE

ETHE

ETHERNET_TX-

ETHERNET_CT

J0JHC0000118

LB9005

G_MR_RESET

CLK_CPIC_SDA

*

R9043

*

C9029

50V

C9002

*

F1G1C104A146

C9035

16V

*

C9017

16V

R9000

*

R9002

*

5

6

4

1

2

3

9

11

13

14

12

10

7

8

IC9001

*

R9001

*

R9025

*

R9024

*

CK9013

CK9016

CK9022

CK9023

CK9002

CK9019

*

C9014

16V

CK9017

CK9018

R9003

*

CK9021

R9004

*

*

R9005

R9019

*

C9003

*

*

C9015

16V

*

C9005

*

C9032

C9001

*

CK9020

CLK_ALLPLAY_LRCK

CLK_ALLPLAY_SDOUT

CLK_ALLPLAY_BCK

CK9015

*

C9013

16V

R9039

*

CK9014

*

R9040

CK9012

*

R9012

R9010

*

*

R9011

6

7

T1

5

2

4

3

8

ThermalPad

1

IC9002

*

CLK_CPIC_SCL

*

C9012

16V

6

7

5

9

25

24

26

21

20

22

17

18

13

10

12

11

16

14

15

19

23

28

27

8

1

3

4

2

29

30

*

CN9000

*

LB9002

PW_D3R3V

LB9003

*

R9023

*

C9033

*

C9039

F1H1H104B047

50V

R9042

*

R9041

*

DGND

1

2

5

6

3

4

IC9004

*

ASRC_AGND

*

C9020

16V

*

C9021

6.3V

R9014

*

R9015

*

R9035

*

R9018

*

*

R9031

G9000

*

C9019

16V

*

C9028

16V

*

C9022

10V

R9017

*

R9016

*

C9023

*

50V

R9029

*

2

1

29

7

24

8

23

5

4

26

27

6

25

16

15

13

11

9 10

12

19

20

18

22 21

14

17

3

28

30

*

IC9003

R9021

*

R9022

*

R9020

*

*

C9025

50V

CLK_ALL_DATA

PLL0

PLL1

UNLOCK

IDIF0

SDTI

IBICK

IDIF2

IDIF1

OBIT1

H

OBIT0

H

CMODE1

H

H

H

ODIF0

ODIF1

CMODE2

CMODE0

L

L

SDTO 24bit

OLRCK AND OBICK INPUT, FREQ >=48fso

OUTPUT AUDIO INTERFACE FORMAT

I2S COMPATIBLE

SLAVE

OMCLK NOT USED

fso = 8k - 216KhZ

CMODE0

CMODE1

OBIT0

OBIT1

IMCLK

ODIF1

ODIF0

CMODE2

TO I/O EXPANDER IC (p21)

FROM SELECTOR 4 (@ DSP)

TO I/O EXPANDER IC (p20)

H

H

L

L

L

H

SPI_MOSI

SPI_MISO

SPI_CLK

PW_3R3V_MR

HS_UART_TX

MR_GPIO11

GND

MR_GPIO12

HS_UART_RX

1OE

VCC

GND

GND

GND

USBDATA_DPP

SPI_CS

GND

GND

MR_GPIO04

2Y

3A

1Y

2Y

VCC

GND

1A

2A

GND

3Y

PW_3R3V_MR

USB_DATA_DPM

1A

4OE

MR_BCK(I2S)

4Y

2OE

2A

3OE

1Y

4A

MR_MCLK(I2S)

MR_LRCK(I2S)

CONN2

MR_DATAIN(I2S)

MR_DATAOUT(I2S)

GND

PW_3R3V_MR

GND

GND

GND

GND

RESET

I2C_SDA

NC

I2C_SCL

NC

NC

MR_GPIO15

PW_3R3V_MR

VCC

VSS

JTAG_TCK

MR_RST

JTAG_TDI

FETX0_DPM

FETX0_DPP

CONN1

FERX0_DPM

JTAG_TMS

MR_TXD=>

MR_RXD<=

JTAG_TDO

PW_3R3V_MR

PW_3R3V_MR

FERX0_DPP

PW_3R3V_MR

PW_3R3V_MR

V_ETH_CTAP

MR_SCL(I2C)

MR_SDA(I2C)

IDIF1

PLL2

IDIF0

TO SOC IC (p121/p122)

CT

CT

GND

NC

TX+

TX-

RX-

RX+

TO I/O EXPANDER IC (p23)

TO MAIN SUPPLY (ALLPLAY DCDC 3.3V)

IDIF2

TO I/O EXPANDER IC (p22)

TO SELECTOR 4 (@ DSP)

Route pair between TX+ and TX-

Also between RX+ and RX-

Impedance Control 100 ohm

PLL0

PLL1

24/16 bit I2S COMPATIBLE INPUT

IBICK freq >= 48 fsi or 32fsi

SLAVE

ILRCK 16k-216kHz

IBICK depend on IDIF2-0

IMCLK not used, Semi auto SMUTE

DVSS

AVDD

SDTO

DVDD

OLRCK

OBICK

OMCLK

PDN

SMUTE

FILT

AVSS

DITHER

PLL2

ILRCK

TO MAIN ETHERNET