102

15

16

17

18

19

20

21

22

23

24

25

26

27

28

B

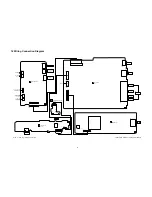

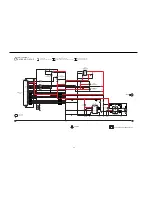

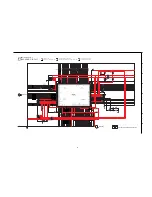

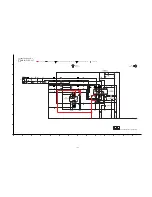

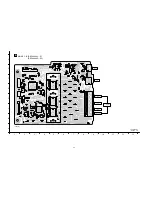

MAIN CIRCUIT

SCHEMATIC DIAGRAM - 8

SA-XH50P/PC MAIN CIRCUIT

3/8

4/8

7/8

2/8

6/8

8/8

1/8

5/8

TO MAIN

CIRCUIT (1/8)

TO MAIN

CIRCUIT (3/8)

TO MAIN

CIRCUIT (6/8)

P1

P1

A

TO

BACKEND CIRCUIT

(FP8101)

IN SCHEMATIC

DIAGRAM - 6

50

1

: MUSIC PORT/AUX/TUNER AUDIO INPUT SIGNAL LINE

: -B SIGNAL LINE

: +B SIGNAL LINE

: FM SIGNAL LINE

: AUDIO OUTPUT SIGNAL LINE

0.1

C400

R431

47

R432

47

16V10

C406

0.1

C407

C420

16V10

R430

47

R419

47

0.1

C421

PWM_CENT-

P

PWM_SUBW-

VALID

P

47

R421

R416

47

R420

47

PWM_FR-

47

R422

47

R423

PWM_FL-

R417

47

R424

47

R418

47

0.1

C417

DAP_CLK

SRCK

R409

47

LRCK

C412

0.1

C411

0.1

R407

47

R408

47

R406

47

DAP_SDA

SDATA0

SDATA2

R410

47

R414

10K

SDATA1

R412

47

R413

47

47

48

44

45

40

41

36

33

35 34

38

39

37

43 42

46

1

62

63

58

57

60

61

59

64

53

50

49

52

51

55

56

54

8

7

9

4

6

5

23

24

21

18

19

17

20

22

16

12 13

10 11

15

14

2

3

31

29

30

32

27

28

25

26

IC401

C1AB00003216

0.1

C416

47

R403

DMIX

220

R401

0.1

C402

0.01

C453

DAP_RST

C408

16V10

PW_3.3V_D

PW_3.3V_DAP

DAP_PDN

1K

R436

R435

100

J0JYC0000196

L427

DAP_MUTE

3.3

R402

C451

15P

C452

15P

0.1

C405

0.1

C404

0.1

C403

220

C401

0.1

R400

16V10

C410

C409

1000P

0.01

C414

R495

100

PWM_SR-

PWM_SL-

MCLK

GND

MCLK

RESERVED

VR_PWM

[3] PLL_FLTM

VBGAP

/RESET

[17] VRD_DPLL

AVSS

/PDN

/MUTE

DVSS

DVDD

AVSS

AVSS_PLL

/HP_SEL

VRD_PLL

AVDD_PLL

PLL_FLTP

[1] VRA_PLL

XTL_IN

RESERVED

SCL

SDIN4

SCLK

LRCLK

[31] SDIN1

[32] PSVC

SDIN3

SDIN2

SDA

DVSS

VR_DIG

RESERVED

RESERVED

XTL_OUT

OSC_CAP

VALID

PWM_M_1

PWM_M_3

PWM_M_4

PWM_P_4

PWM_P_3

PWM_P_1

PWM_P_2

PWM_M_2

PWM PROCESSOR

DVDD

DVSS

/BKND_ERR

DVSS

[2] PLL_FLT_RET

[50] PWM_P_7

DVSS_PWM

PWM_HPML

PWM_HPMR

PWM_HPPR

PWM_HPPL

DVDD_PWM

PWM_P_8

PWM_P_5

PWM_P_6

PWM_M_6

PWM_M_5

PWM_M_8

[49] PWM_M_7

R411

0

1M

R404

10P

C415

C413

10P

2

GND

3

1

4

GND

X400

H0J135500050

LRCK

0

R283

0

R284

0

R285

0

R293

0

R292

0

R291

0

R282

SDATA2

CEC_IN_OUT

PW_3.3VREF

SDATA0

SDATA1

REV

AMUTE

0

R268

0

R278

0

K105

0

R269

0

R289

0

R273

VBUS_EN

DVD_TX

DVD_RX

FWD

CLOSE_SW

OPEN_SW

USB_OC

0

R290

0

R280

TV_R

TV_L

AGND

0

R288

0

R281

0

R279

0

R271

0

R277

0

R276

0

R275

L292

J0JYC0000196

L291

J0JYC0000196

0

R274

K153

K155

K154

0

K158

K156

0

0

0

0

SRCK

DMIX

0

R286

0

R287

6

7

5

9

47

44

39

40

35

31

27

24

21

20

22

16

15

18

17

11

13

12

10

14

19

23

26

25

30

28

29

34

32

33

38

36

37

43

41

42

46

45

49

48

8

1

3

4

2

50

CN201

PW_SW5V_D

0

R272

0

L290

0

R270

I2S_IN

0

R296

0

R295

VGND

MGND

PW_VREF

CEC IN/OUT

SPIDIF_SW

MCLK

DGND

DGND

M+9V

MGND

M+9V

DGND

MGND

RGB_H

ADGND

ADGND

DGND

LRCK

BICK

DGND

DGND

PW_9V

SDATA2

SDATA0

SDATA1

D+5V

D+5V

I2S_IN

D+5V

SDATA3

D+5V

TV_LIN

FUNC_SW

TV_RIN

D+5V

D+5V

D+5V

SPIDIF_OUT/GND

DGND

ADGND

AMUTE

VBUS_EN

USB_OC

MIC_IN

CLOSE_SW

FWD

REV

UART_TX

OPEN SW

UART_RX

iPod_VIDEO

VGND

iPod_SW

SPDIF SW

Summary of Contents for SA-XH50P

Page 13: ...13 4 1 Others Licences ...

Page 16: ...16 5 4 Speaker Connection ...

Page 17: ...17 5 5 Linked Operations with the TV VIERA LINK HDAVI Control ...

Page 18: ...18 ...

Page 19: ...19 5 6 Connection with an ARC compatible TV ...

Page 21: ...21 5 7 2 File Extension Type Support MP3 JPEG ...

Page 23: ...23 3 Gently pull out the tray 4 Remove disc ...

Page 46: ...46 10 2 Main Components and P C B Locations ...

Page 82: ...82 ...

Page 92: ...92 ...

Page 94: ...94 ...