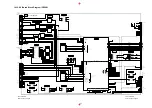

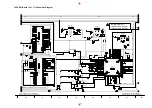

14.25. DG-Board (1 of 2) Block Diagram

AFC1

LED_R

SOS2

M2_RST

B_DDR_CLK

B_DDR_NCLK

RM_IN

SP_MUTE

KEYSCAN

XB

UF

M2_RST

CVBS1

AV2_QLINK

RGB_FB

TUNER_MAIN_ON

SOS

Q_LINK_IN

Q_LINK_OUT

Q_LINK_SEL

MAIN_Y/CVBS

MAIN_PB/C

MAIN_PR

AV4_QLINK

AUDIO_MUTE

BS_R

DVB_CVBS

BS_L

SD_LED

MAIN_PR

RGB_CVBS

MAIN_PB/C

MAIN_Y/CVBS

SRQ

TO

H2

DG2

SELF,ID,ED2

1080i

A/D 10bit

VPK

COLOUR

30MHz

30MHz

A/D 10bit

Macrovision

625i/p

A/D 10bit

MATRIX

NOISE LEVEL

RGB->

YUV

CHROMA

720p

Sync

SEPA

30MHz

Detection

3D/2D com

525i/p

SYNC

CLK

SW

TBC

I/F

FF

IP

NR

JUST

NR

I/P

FF

IC4005

10bit A/D

22

UV0~UV9

29

76

SOS2

10

STB_RESET

13

SCL2

21

SDA3

23

SP_MUTE

12

SOUND_MUTE

11

AV2_QLINK

FB_OUT 26

1

2

RMCN

AV4_QLINK

AFC1

3

6

LED_R 15

2

3

DG20

1

TO

PA20

25

23

MAIN 3.3V

SOS

BT30V

AC_ON/OFF

DG MICOM,DIGITAL SIGNAL PROCESSOR

22

20

18

17

15

13

12

9

7

5

MAIN 3.3V

SUB 3.3V

SUB 9V

SUB 9V

MAIN 2.5V

MAIN 2.5V

SUB 5V

MAIN 5V

STB 5V

SUB 5V

MAIN 5V

STB 5V

4

RESET

IC4063

SDA2

SDA

NRST

IC4055

128M DDR SDRAM

3

4

TVON

MAIN 9V

MAIN 3.3V

SUB 9V

MAIN 9V

74

72

Q4006,Q4013

Q4011

Q4012

38

XTAL

20

24

KEYSCAN

8

A_DDR_CLK

A_DDR_NCLK

IC4054

GC4PRO

SDA2

SCL3

SCL3

SDA2

SCL2

SDA3

CLK0A

CLKIA

HSIA

VSIA

TPOUT0

7

Y0~Y9

14

R0~R3

33

30

41

42

91

94

R0~R3,Y0~Y9,UV0~UV9

SDA2L

SDA

SCL2L

81

SCL

82

D_CLKIN

RESET

VS

HS

LLC1

(ADV7403)

PORT-A

1

SDA1

18

17

SCL1

DEM.

DETECT

Q4068

9

SRQ

35

36

4

99

78

AVR 3.3V

8

VOUT 1

IC4049

CONT

AD 3.3V

5

VIN

SUB 5V

VOUT

PLL 1.2V

AVR 1.2V

MAIN 2.5V

1

IC4044

VIN

5

VOUT

AVR 1.2V

1

IC4061

VIN

5

DLL 1.2V

Q4010,Q4015

57

Q1153

Q1152

Q1151,Q1150

4

2

5

3

IC1105

Q LINK SW

1

13

51

6

3

2

SDAIN

7

SCLOUT

IC1235

SDAOUT

SCLIN

IIC BUFFER

SCL1

SDA1

Q1154

AIN9

FB

Q4900

2

INV.

RGB_CVBS

SD_LED

17

33

DVB_R

DVB_CVBS

31

DVB_L

TO

H1

35

DG1

MAIN_CVBS2(RGB)

MAIN_PR/B

28

30

32

MAIN_Y/V/G

34

MAIN_PB/C/R

STB 5V

14

STB 5V

VDD

AVR 2.5V

VCC

VOUT

VOUT

4

IC4024

3

5

IC4042

AVR 1.8V

4

1

OUT

STB 5V

2

1

IC1103

1

AVR 1.8V

3

MAIN 3.3V

VDD

2

AVR STB 2.5V

STB 2.5V

AVR 3.3V

AD 3.3V

STB 5V

4

MAIN 2.5V

MAIN 1.8V

DDR 2.6V

MAIN 5V

VIN

IC4008

4

VIN

5

VDET

VOUT

AVR 3.3V

VIN

VOUT

MAIN 1.2V

IC4048

AD 1.8V

AVR 1.2V

MAIN 3.3V

IC4041

2

AVR 2.6V

5

VIN

VO

VCC

VOUT

STB 3.3V

5

OUT

IC1110

MAIN 2.5V

MAIN 2.5V

1

MAIN 3.3V

IC4025

SCL

SCL2

(FS&HDMI)

PORT-B

PE50B ONLY

TH-37/42PA50E, TH-37/42PE50B

DG-Board (1 of 2) Block Diagram

TH-37/42PA50E, TH-37/42PE50B

DG-Board (1 of 2) Block Diagram

91

Summary of Contents for TH-42PA50E

Page 5: ...1 Applicable signals 5 TH 42PA50E TH 42PE50B TH 37PA50E TH 37PE50B ...

Page 17: ...7 Location of Lead Wiring 7 1 Lead of Wiring 1 17 TH 42PA50E TH 42PE50B TH 37PA50E TH 37PE50B ...

Page 18: ...7 2 Lead of Wiring 2 18 TH 42PA50E TH 42PE50B TH 37PA50E TH 37PE50B ...

Page 19: ...7 3 Lead of Wiring 3 19 TH 42PA50E TH 42PE50B TH 37PA50E TH 37PE50B ...

Page 22: ...8 3 No Picture 22 TH 42PA50E TH 42PE50B TH 37PA50E TH 37PE50B ...

Page 25: ...25 TH 42PA50E TH 42PE50B TH 37PA50E TH 37PE50B ...

Page 26: ...9 3 Option Description 26 TH 42PA50E TH 42PE50B TH 37PA50E TH 37PE50B ...

Page 27: ...27 TH 42PA50E TH 42PE50B TH 37PA50E TH 37PE50B ...

Page 31: ...10 5 Test Point Location 31 TH 42PA50E TH 42PE50B TH 37PA50E TH 37PE50B ...

Page 36: ...36 TH 42PA50E TH 42PE50B TH 37PA50E TH 37PE50B ...

Page 37: ...14 Block and Schematic Diagram 14 1 Schematic Diagram Notes 67 ...

Page 38: ...14 Block and Schematic Diagram 14 1 Schematic Diagram Notes 67 ...