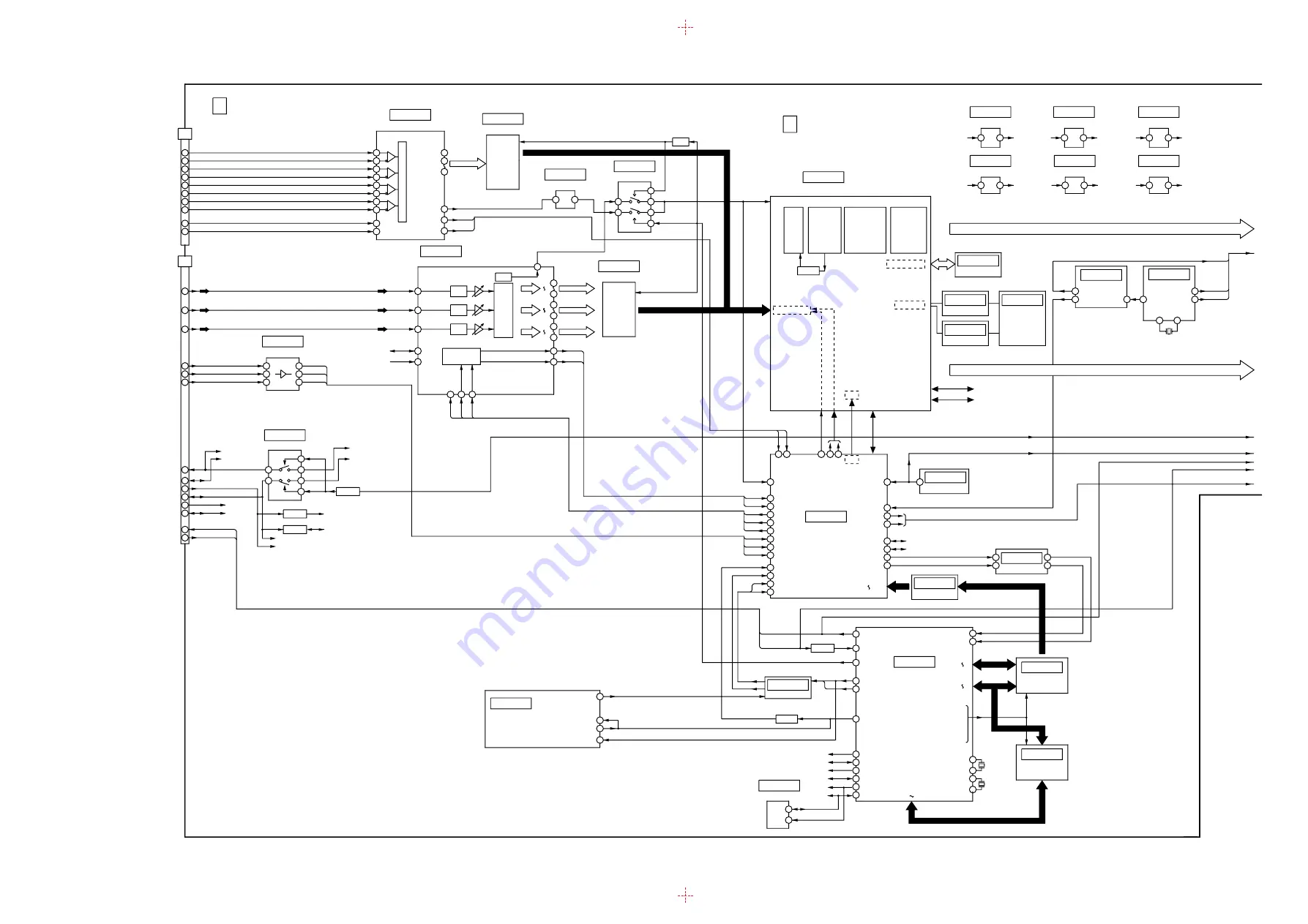

14.39. D-Board (1 of 2) Block Diagram

1

SDA1(IIC 5V)

5

Q9719

St-r

4

5V->3.3V

IIC_CONT

/Y Pb Pr

3.3V

5V->3.3V

IC9151

IIC_CONT

OSC IN

COLOR

OSC OUT

FORMAT CONVERTER(I/P)

NV IN

2

D00

PLL M

8BIT

WB-Adj

A0

30

8BIT

A9

36

CTI/TINT

IC9605

IC9009

G

D15

HD

IC9157

48

CLP C1

R

WE

56

VD

F.CLP

40

SERIAL

38

OE

CLK

110M

57

VD

31

RAS

CONVERTER

DG3

OSD

5

CAS

RGB

SCL2

VDS I/O

8

CE

OSD

G0

19

77

5V->3.3V

(100MHz)

5

Y/G IN

PR S

DATA

IC9023

6

SDRAM I/F

70

OSD

SCL

CONTRAST

54

SDA2

SDA

CLP

ADC

43

Y S

23

IC9702

HS

FORMAT

HD

B7

HDS I/O

EEPROM

3.3V->5V

CLAMP

Q9707

VS

IC9154

VS OUT

SDA1

8

SDA3

5V->3.3V

SYNC/SEPA

PB S

CLP

SCL2

IC9014

SDA2

SCL1

HS C1

SDA2

DIGITAL C

D3

R(8Bit)

3

SDA1

32

A/D CONVERTER(SUB)

DCKC

HD

SCL3

9

VD

VS C1

SCL1

66

SCL2

OCK PLL

SCL3

7

R0

34

64M SDRAM

SDA3

HD S

27

IC9155

CABLE_DET

DCKC

64

55

B0-B7,G0-G7,R0-R7

REG 3.3V

VD S

B

1

IC9001

27

VRAM(1Mbit)

CLKC

G7

SOUND MAIN MUTE

P5V

29

NCLP

IC9704

12

5

9

38

FLASH MEMORY

SMM

4

Pr/R IN

IC9705

CABLE DET

3.3V

VD

(8M ROM)

13

REG 3.3V

CLP

CABLE DET

IC9006

SMM

12

TXC-

15

P5V

VS OUT

D-Board(1of2)Block Diagram

SCL3

17

5

26

B(8Bit)

Q9704

13

4

D

TXC+

Q9703

HS OUT

3.3V

Format Converter

3

SCL2(3.3V)

LEFT(MASTER)RGB 8bit

HSYNC

REG 3.3V

D6

SDA2(3.3V)

D

ADC

IC9007

19

(1/2)

132

Pb/B IN

5

P5V

12

SDA1

133

TO DG-BOARD

9

3

5

SCL1

SCL2

CLP

7

CLK OUT

7

SDA2

G

4

Q9001

6

18

B

CLP

SCL2

17

R

HD

17

SDA2

SCL I/O

2

87

16

SDA I/O

IC9711

88

TX2+

MCVD

SDA1

7

TX0+

(I/P

SDA2

MCHD

5

8

CONVERTER)

SCL1

20

LVDS:Low Voltage Differential Signaling

SCL2

TX1-

38

12

39

TTL P

ARALLEL

T

O

L

VDS

OSC OUT

6

OSC IN

TX3+

113

TX3-

100

IC9002

71

2

106

3

4

18

61

6

206

BUS SWITCH

70

IC9004

11

NH IN

3

205

11

AD1

1

15

MICRO PROCESSOR

7

15

SDA3

2

IC9003

IC9706

5

2

SCL3

OE

5

SOUND MUTE

IC9008

4

67

B0-B7,G0-G7,R0-R7

14

9

BUS SWITCH

IC9606

PLL

R/G/B

RIGHT(SLAVE)RGB 8bit

10

OE

RESET

INV.

89

110M

RESET

9

90

G(8Bit)

3.3V->5V

TX2-

68

77

24

IC9703

10

111

31

SYNC PROCESSOR

15

HS OUT

VSYNC

17

TX0-

B0

3

IC9005

SDA3

5

9

R7

5V->3.3V

TX1+

3

IC9602

6

SCL2(IIC 5V)

3

IC9153

REG 5V

1

5V

UNREG 14V

P5V

REG 3.3V

5

4

IC9152

3.3V

5

4

P5V

IC9302

3.3V

REG 3.3V

LVDS/TTL(PARALLEL)

INVERTER

SWITCHING

SWITCHING

SDA2

SCL2

X9701

X9703

OSD IN0

(1/2)

24.5MHz

SMM

OSD

74

75

185

RESET

OSD IN7

CABLE_DET

A01

A19

20MHz

SDA2

SCL2

SCL2

SDA2

R/G/B

182

179

178

1

6

PLL

IC9301

5

CLK2

CLK1

XIN

IC9303

PLL

X OUT

8

OSC

6

CLKE

4

5

IN

OUT

OSC

CLKD

7

50MHz

A/D SEL.

HD,VD

CLK

VD

HD

X9302

20MHz

60MHz

65MHz

50MHz

MC CLK

85

104

FPGA-LD

5V<->3.3V

IC9701

21

20

MC CLK

FPGA-LD

147

RESET

16

MCDATA

RESET

MCDATA

IC9709

42

(1/2)

SUB MPU(CONVERTER)

RESET

SW

Q9706

86

MCCLK

10

11

9

LSI RESET

RESET

DATA IN

DATA OUT

MC CLK

(1/2)

HDD

VDD

DCKS

50MHz

CLK

TH-42PX20U-P D-BOARD (1 of 2) BLOCK Diagram

TH-42PX20U-P D-BOARD (1 of 2) BLOCK Diagram

101

Summary of Contents for TH-42PX20U/P Operating

Page 9: ...6 2 Lead of Wiring 2 9 ...

Page 10: ...6 3 Lead of Wiring 3 10 ...

Page 11: ...6 4 Lead of Wiring 4 11 ...

Page 12: ...6 5 Lead of Wiring 5 12 ...

Page 34: ...15 2 Parts Location 2 34 ...

Page 35: ...15 3 Parts Location 3 35 ...

Page 36: ...36 ...

Page 37: ...15 4 Parts Location 4 15 5 Parts Location 5 37 ...

Page 38: ...38 ...

Page 42: ...17 2 Electrical Replacement Parts List 42 ...

Page 54: ...D12 K1KA07A00189 7P CONNECTOR 1 54 ...

Page 348: ...1 Applicable signals 4 TH 42PX20U P ...

Page 353: ...6 Location of Lead Wiring 6 1 Lead of Wiring 1 9 TH 42PX20U P ...

Page 354: ...6 2 Lead of Wiring 2 10 TH 42PX20U P ...

Page 355: ...6 3 Lead of Wiring 3 11 TH 42PX20U P ...

Page 356: ...6 4 Lead of Wiring 4 12 TH 42PX20U P ...

Page 357: ...6 5 Lead of Wiring 5 13 TH 42PX20U P ...

Page 358: ...6 6 Lead of Wiring 6 14 TH 42PX20U P ...

Page 367: ...9 4 IIC mode structure following items value is sample data 23 TH 42PX20U P ...

Page 376: ...32 TH 42PX20U P ...