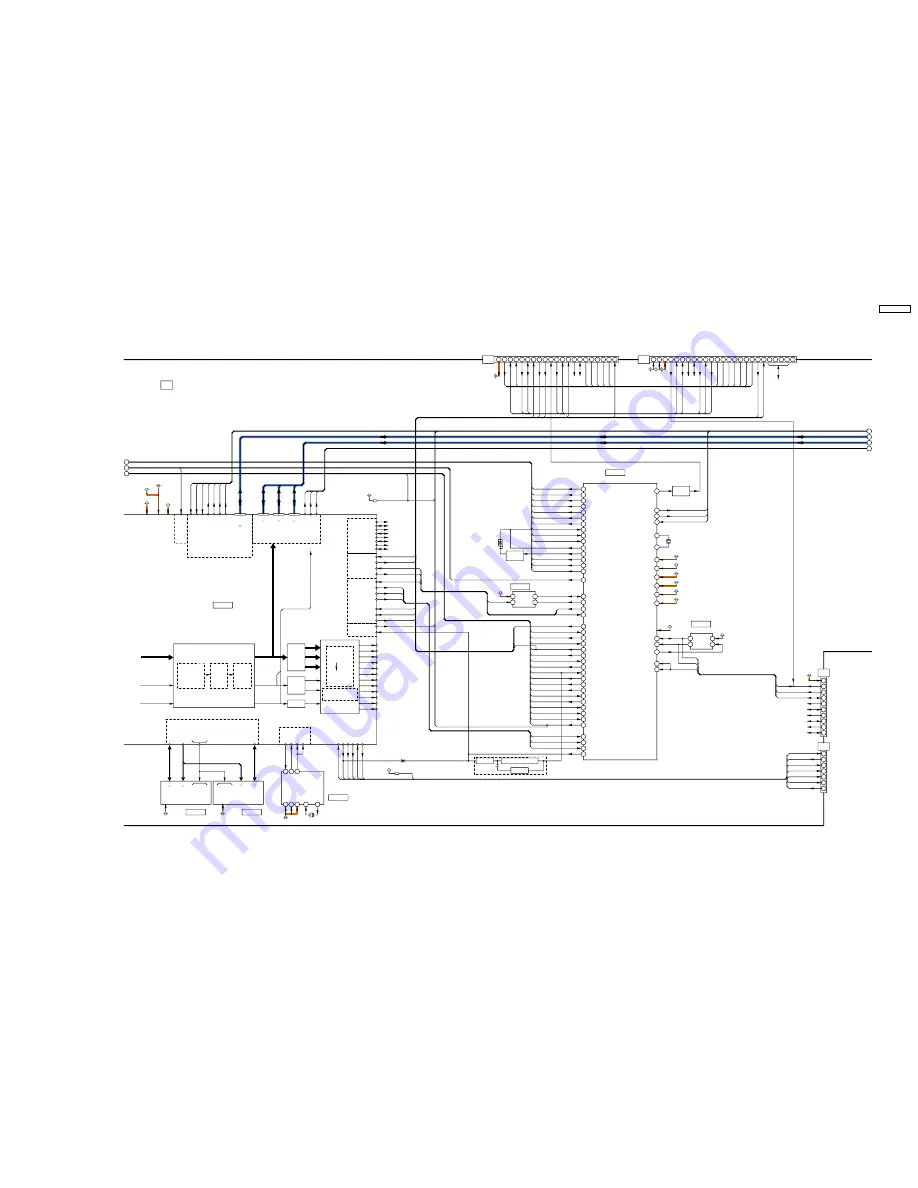

15.25. DG-Board (3 of 4) Block Diagram

SBI2

SBO2

SCL

SDA

HPD3

7493_XRST

HDMI_5V_DET1

HDMI_5V_DET2

HDMI_5V_DET3

EDID_WP

7493_XRST

KEY1

FAN_SOS

FAN_MAX

SOUND_SOS

SOS

A_MON_MUTE

AUDIO_MUTE

AUDIO_XRST

RMIN

R_LED_ON

KEY3

AI_SENSOR

DTV_XRST

FPGA_XRST

CONFIG_DONE

SLRCK

SD_ERROR

ADCCK

HDMI_CEC

TV_SUB_ON

SD_ERROR

SLRCK

ADCCK

ECO_ON

PANEL_STATUS

PANEL_SOS

PANEL_MUTE

PEAKS_OSHO

PEAKS_OSCK

O

PEAKS_OSV

O

PEAKS_YM

PEAKS_YS

PEAKS_OSDH

PEAKS_OSDCK

MHSYNC

MVCLK

VHSYNC

EEPROM_WP

SBO0

SBI0

SBI2

SBO2

EEPROM_WP

RF_AFT

HPD2

STB_RST

SD_LED_ON

TV_MAIN_ON_DELAY

FE_XRST

D_TXD

ECO_ON

D_RXD

P

ANEL_SD

A

P

ANEL_SCL

D_PSTB

D_IIC_CONT

D_PB

USY

D_PDB0

D_PSLCT

D_PDB1

D_IIC_INT

SBO0

P

ANEL_SOS

SBI0

P

ANEL_ST

A

TUS

P

ANEL_MUTE

P

ANEL_SD

A

P

ANEL_SCL

D_IIC_INT

D_RXD

D_PDB1

D_15V

D_TXD

D_PSLCT

D_PDB0

D_PB

USY

D_PSTB

TV_SUB_ON

D_IIC_CONT

D_15V

SRQ1

SCL

SDA

OSD_FLAG

LVDS_PD

LITE2_RX

XRST

POWER_DET

FORMAT_EDGE

TV_MAIN_ON

LITE2_TX

SDBOOT

SDBOO

T

XRST

LITE2_TX

FORMA

T_EDGE

LITE2_RX

HPD1

HDMI_MUX_SEL

HDMI_MUX_EN

HDMI_REP_EN

TV_MAIN_ON

TV_MAIN_ON

TV_MAIN_ON

HQ1_XRST

HQ1_XRST

SRQ1

PO

WER_DET

X8001

D8600

AUDIO_XRST

GAMMA

106

SP_MUTE/A_MON_MUTE

21

7493_XRST

I/P CONV.

EEPROM

126

EDID_WP

93

53

SCL0

7

NRST

AI_SENSOR

33

38

8

39

NR

H

40

113

MIX

35

HPD3(IRQ8)

HQ1_XRST

124

Q1107

SCL3

RESIZE

SDA0

70

X1100

CONV.

49

68

65

DTV_XRST

SDA3

CECO

84

114

83

R_LED_ON

OSCXI

V

SBI0A

RMIN

SOS(ADIN3)

69

111

45

AI

RF_AFT(ADIN0)

HDMI_5V_DET1

SBO0A

D/A

HDMI_CEC_PU_ON

FAN_MAX

86

OSCXO

TC1N

TCLK1N

TA1N

TE1N

TD1N

TD1P

DATA

TE1P

TB1N

TC1P

LVDS IF

TCLK1P

TTL

TB1P

TA1P

PARALLEL

115

FAN_SOS(ADIN6)

KEY1(ADIN4)

117

2

ECO_ON

SOUND_SOS(ADIN7)

118

KEY3

18

MAIN MICOM

5

8

6

SRQ1

1

7

4

9

GENX_SCL1

GENX_SDA1

2

STB5V

10

LITE2_SCL3

LITE2_SDA3

11

LITE2_SCL1

LITE2_SDA1

LITE2_SCL2

LITE2_SDA2

DG18

SCL1

SDA2

SDA1

SCL3

SDA3

SCL2

STB5V

6

5

VCC

WC

SDA

SCL

54

HDMI_5V_DET2

55

HDMI_5V_DET3

7493_NRST

69

TV_SUB_ON

1

17

SD_LED_ON

127

AUDIO_MUTE

CONFIG_DONE

FPGA_XRST

59

122

SLRCK

24

SD_ERROR

110

ADCCK

52

DTV9V

SUB5V

30

27

SUB5V_SENSE

STB5V_SENSE

MAIN5V_SENSE

34

STB5V

29

DTV9V_SENSE

66

MAIN9V_SENSE

SUB5V

MAIN9V

SCL0

SDA0

SCL1

SDA1

SCL2

SDA2

SDA3

SCL3

SCL0

SCL3

SCL1

SDA0

SDA1

SDA2

SDA3

SCL2

SBI0

SBI2

SBO0

SBO2

EEPROM_WP

ADCCK

SLRCK

SD_ERROR

DSRCK/VMUTE

PANEL_STATUS

PANEL_SOS

SERIAL

LVDS

DATA

DIFFERENTIAL

OUTPUT

TRANSMITTER

LVDS

x3

10bit

8bit

D/A

R

G

B

(XECS5)

(SBT0)

(XECS3)

(SBT2)

I/F

IIC

I/F

SERIAL

PORT

COMMON

CLK

D/A

R

OE2

R

OE9

GOE2

GOE9

BOE2

BOE9

PIXEL

DIGITAL VIDEO PROCESSOR

MVCLK

MHSYNC

MVSYNC

(V

OP22)

(V

OP29)

(V

OP12)

(V

OP19)

(V

OP2)

(V

OP9)

LOSDOUT0

LOSDOUT15

(VI2P9)LOSD_H_I

(VI2P8)LOSD_CLK_I

(VI2P7)LOSD_V_I

(VI2P6)LOSDOUT_YM

(VI2P5)LOSDOUT_YS

(VI2P2)LOSDOUT_CLK

O

(VI2P3)LOSDOUT_H_O

LOSD OUT (HQ1)

HQ1L VIDEO

DQ0

DQ15

A12

A0

CS(CS0)

WE,CKE

RAS

,CAS

CK

WE,CKE

RAS

,CAS

DQ15

CK

CS(CS1)

A12

A0

DQ0

1.8VDDR_I/F

1.8VDDR_I/F

DQ0-DQ15

A0-A12

XWE,CKE

XRAS

,XCAS

CK

XCS1,XCS0

DQ16-DQ31

CLOCK GEN

4

27M

7

X1

1

74M

X2

VIN

16

9

VDD

5

15

VDD

VDD

13

SUB3.3V

Q1108

CK27

CK270

VC27

CLK74

SUB3.3V

CLOCK GEN

DDR2-0 512M

DDR2-1 512M

DDR2-0/DDR2-1

BOE2-BOE9

R

OE2-R

OE9

GOE2-GOE9

LOSDO0-LOSDO15

ADDRESS B

US

D

ATA

B

U

S

D

ATA

B

U

S

105

PANEL_STBY_ON

PANEL_VCC_ON

Q4014

Q4015

Peaks Lite2

DIGITAL SIGNAL PROCESSOR

R/G/B

H/V

CLK

R/G/B

H/V

CLK

MAIN3.3V_SENSE

MAIN3.3V

67

IS1CLK

IS1DATA

(VI2ENB)

(VI2P10)

(VI2P21)

37

HPD2(IRQ7)

Q4013

Q4011,Q4012

Q4010

12

SW_OFF_DET

SW_OFF_DET

IS I/F

STB3.3V

IVDD

TV_MAIN_ON_DELAY

71

XECS6

POD.CI I/F

USE

FOR

FACTORY

IC8003

IC1103

IC8002

IC8004

IC8001

IC8503

DIGITAL SIGNAL PROCESSOR

DG

MICOM

HDMI INTERFACE

SUB1.2V

1.8VDDR_I/F

SUB1.8V

SUB3.3V

D_15V

18

17

CFG_JT

A

G

2

SBI0

D_PDB0

3

IIC_SCL1

D_PDB0

4

TO

STB5V

D_PSTB

D_RXD

LITE2_SD

A0

SBO0

IIC_CONT

19

SD

A0

7

D_15V

19

D_PDB1

D_PSLCT

FACTORY

ALARM

15

21

25

29

IIC_CLK2

CFG_TCK

14

D_PB

USY

4

11

D3

CFG_TMS

CFG_TRST

D_PDB1

26

P

ANEL_SCL

F_SUB_ON

STB5V

30

FOR

1

10

CFG_TDI

16

D_IIC_INT

22

IIC_CONT/

SRQ

ECO_ON

IIC_SD

A1

DG35

22

P

ANEL_STBY/

VCC_ON

SUB3.3V

DG17

D_TXD

15

IIC_D

A

T

A2

21

6

D_PB

USY

D_IIC_INT

23

16

D_PSTB

STB3.3V

14

6

LITE2_SCL0

STB3.3V

D_PSLCT

SCL0

SCL0

7

SD

A0

STB5V

9

12

P

ANEL_TXD

24

27

8

CFG_TDO

18

D_IIC_CONT

P

ANEL_RXD

1

P

ANEL_SD

A

26

28

29

13

12

STB5V

5

2

USE

8

READ

Y

20

SUB3.3V

DISPEN

SUB3.3V

26

NBOOT

SRQ_GENEX

IC1101

EEPROM

6

5

7

8

VCC

WC

SDA

SCL

STB3.3V

64

63

SDA

SDA1

SCL

SCL1

28

EEP_WP

92

LVDS_EN 15

XRST

LITE2_TX

2

8

7

9

3

TV_MAIN_ON

5

FORMAT_EDGE

LITE2_RX

POWER_DET

SDBOOT

6

DG9

PR

O_XRST

TXD0

SDBOO

T

PO

WER_DET

RXD0

FORMA

T_

EDGE_PR

O

36

HPD1(IRQ6)

HDMI_MUX_SEL

8

HDMI_REP_EN

6

7

HDMI_MUX_EN

SUB3.3V

TO

JG09

13

12

11

21

22

23

24

FULL HD

TH-65PZ750U

DG-Board (3 of 4) Block Diagram

TH-65PZ750U

DG-Board (3 of 4) Block Diagram

TH-65PZ750U

101

Summary of Contents for TH-65PZ750U

Page 5: ...1 Applicable signals 5 TH 65PZ750U ...

Page 24: ...8 Location of Lead Wiring 8 1 Lead of Wiring 1 24 TH 65PZ750U ...

Page 25: ...8 2 Lead of Wiring 2 25 TH 65PZ750U ...

Page 26: ...8 3 Lead of Wiring 3 26 TH 65PZ750U ...

Page 27: ...8 4 Lead of Wiring 4 27 TH 65PZ750U ...

Page 28: ...8 5 Lead of Wiring 5 28 TH 65PZ750U ...

Page 32: ...9 4 No Picture 32 TH 65PZ750U ...

Page 39: ...11 4 Adjustment Volume Location 11 5 Test Point Location 39 TH 65PZ750U ...

Page 41: ...41 TH 65PZ750U ...

Page 77: ...15 Schematic and Block Diagram 15 1 Schematic Diagram Note TH 65PZ750U 77 ...

Page 157: ...16 Exploded Views Replacement Parts List 16 1 Exploded Views 157 TH 65PZ750U ...

Page 158: ...16 2 Packing Exploded Views Accessories 158 TH 65PZ750U ...

Page 159: ...16 3 Replacement Parts List Notes 159 TH 65PZ750U ...