XFERSTO

XIREQ

XWAIT

XCD2

XCD1

CHSYNC

CHVAL

CHCLK

SBO1

SBI1

SPEN

SPCLK

XFERSTO

SPPKTST

SBO1

SBI1

SPEN

SPCLK

SPPKTST

X8003

X8006

VCXO 27MHz

1

TS BUFFER

NOR FLASH ROM

STROUT

CONTROL BUFFER

SDA

9

5

OP AMP

52

EA0

MIBAL,MCLKI

11

I/F

10

67

41

1

V_SUPPLY

21

HDSL PEAKS_Lite

36

50

8

7

66

SW

XCD1,XCD2,XWAIT,XIREQ

ANT_V_SUPPLY

8

(COMMON

VIN

IF_AGC

CIPOWER

VOUT

23

62

16

TU8001

XCD2

2

Q8101

20

CHCLK,CHVAL,CHSYNC

XTALI

4

10

MMA0

D4

VCC

63

INV

XECSO-XECS5

7

VOUT

29

CI SLOT

CVBS

XECSO,XERE

3

MMDQ31

15

SCL

XDACRST

CLKOUT

2

3

PDN

MMDQ0

STROUT

VDD

62

36

FB

DDR-

RESET

XEWE2,PWP

CIRESET

SDRAM

DC-DC CONV.3.3V

XTALO

1

DACCK

D/#P

PVIN

37

2

63

38

256M DDR_SDRAM

HSCLKIN

XRST

46

SUB 5V

LRCK

VC27

57

6

MVCLK0

51

IMM

25

HSSYNCIN

SUB 5V

105

58

43

DMIX

54

1

DL(BS_L)

OUT

9

SUB 9V

7

HSVALIN

53

SUB 9V

CVBS

XIRQ1

2

DR(BS_R)

SDTI

FLG

D7

SCL1

IMP

SUB 9V

10

EA1-EA15

CK27

D0~D7

19

HSDIN0

RESET

A 9V

INTERFACE)

SDA1

MMA13

AOUTR

12

DATA

SUB 5V

10

XIREQ

7

SBI1(SBO1)

17

42

XWAIT

20

COFDM DEMODULATOR

56

AUDIO DAC

LOCK/OP2

6

MVC7

47

SBO1(SBI1)

2

MVY7

MDO0~MDO2

53

EA24

REG#

30

AGC1

IN

11

MVC0

42

SPDATA0~7

6

MVY0

XIORD,XIOWR

MDO3~MDO7

SDA

BICK

MOVAL,MOSTRT

MISTRT

XWE,XOE,REG

MVCLK0

88

LRCK

21

MCLK0,WAIT#

16

MVSYNC0

45

18

4

CD1#,CD2#

LOGIC,

DATA

MHSYNC0

D0

IREQ#

BOOTSWAP,XEDK

MVY0

MVC0

1

IORD#,IOWR#

MVC7

2

JK8401

ADDRESS

OE#,WE#

MVY0

CE1#,CE2#

MVY7

34

XECS3

A0~A14

TO DG1

CONTROL

ED16-ED23

RESET

32

57

CARD 5V

14

VCC

ED31

97

ELLK,XEWE2,XEWE3

29

Vpp1,Vpp2

CONTROL

64

109

CONTROL BUS

TS BUFFER

106

SPEN,SPCLK

ADDRESS BUS

D3

BUFFER

OUT

DATA

107

1

DATA BUS

61

AOUTL

BUFFER

MVSYNC0

4

XERE,ERXW

6

XIRQ2

CONTROL BUS

MHSYNC0

CTL

SCLT

5

24.167MHz

BUFFER

ADDRESS BUS

XCD1

MDI0~MDI7

DATA BUS

AVR +2.5V

ED16

8

72

IFD2

18

59

SRCK

9

CI I/F

MVC7

MCLK

44

SCL

SBI1

SDAT

MVC0

4

SBO1

31

MVY7

DVB TUNER

19

DATA BUFFER

IFD1

2

96

ENABLE0

SCHCLK0

SCHDATA0

XFERSTO

CHPSYNC0

VIDEO

OUTPUT

I/F

OUTPUT

AUDIO

I/F

DECORDER

AV

HSDIN7

DECORDER

TRANSPORT

27M

VIN

VOUT

AVR +1.8V

3.3V

7

1

13

14

18

19

XRST

22

51

41

8

52

1

AVDD

VDDQ

VDD33

MAVDD

SVAVDD

DAVDD

MVAVDD

AAVDD

14

9

2

OUT

VDD

4

RESET

1

2

DC-DC CONV.1.2V

PVIN

INV

SW

VIN

2

1

8

FB

4

VDD12

3

2.5V

XV-BOARD

A0-A21

DG0-DQ15

RESET

64M CPU FLASH ROM

WP,WE,CE,OE

XIRQ1

1.8V

3.3V

ADC

COFDM

Core

FEC

3.3V

3.3V

5V

20

20

14

20

20

20

20

3.3V

3.3V

3.3V

5V

5V

5V

5V

CHARGE

PUMP

EN

43

44

38

37

42

41

45

40

39

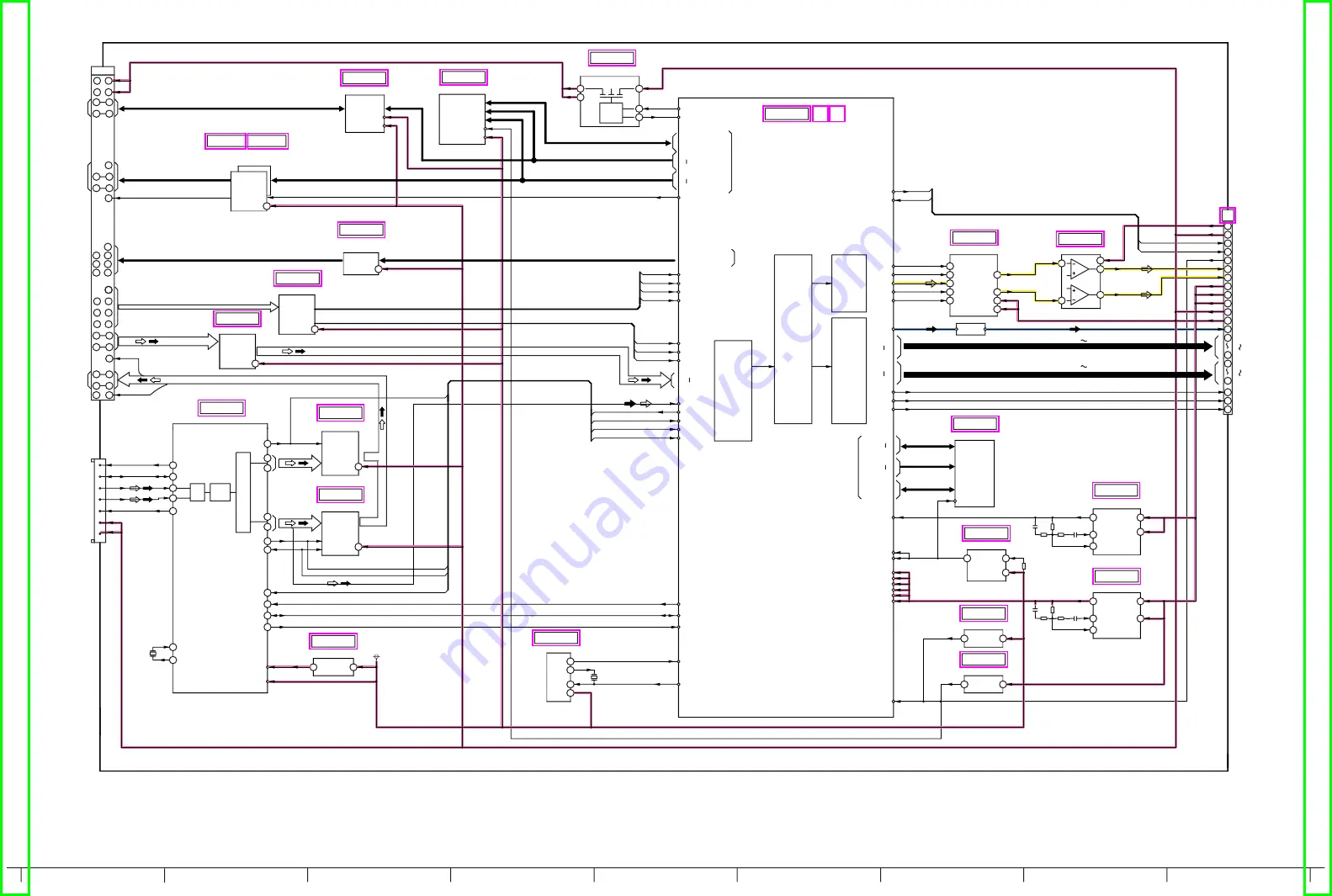

TX-26/32LXD500 TX-26/32LX500F/P

Block Diagram (5 of 7)

TX-26/32LXD500 TX-26/32LX500F/P

Block Diagram (5 of 7)

Summary of Contents for TX-26LX500F

Page 12: ...6 4 Wire dressing 2 Clamping 12 ...

Page 24: ...24 ...

Page 25: ...8 3 Option Description 25 ...

Page 26: ...26 ...

Page 32: ...13 2 Front Chassis Layout 13 3 Cabinet Ass y Layout 32 ...

Page 33: ...13 4 Packing 33 ...

Page 58: ...IC2108 C0EBF0000354 IC 1 58 ...

Page 63: ...L8501 ELJNA2R7JB INDUCTION COIL 1 63 ...

Page 105: ...IC1104 C2CBYF000032 IC 1 105 ...

Page 107: ...IC5015 C0CBCAD00016 IC 1 107 ...

Page 111: ...Q1119 2SA207700L TRANSISTOR 1 111 ...

Page 162: ...11 Schematic Diagram 11 1 Schematic Diagram Notes 35 ...

Page 163: ...11 Schematic Diagram 11 1 Schematic Diagram Notes 35 ...