3DQDVRQLF

10

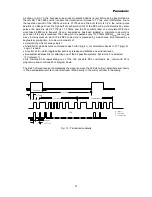

1.1.4 Horizontal and vertical synchronization

See also the related block diagram as well as the diagrams at the end of the report.

The main functions are:

* Horizontal sync separator

* Horizontal oscillator and calibration system

* PHI-1 detector

* PHI-2 detector and sandcastle generation

* Horizontal output with slow start/stop facility

* Coincidence detector

* Noise detector

* Vertical sync separator

* Vertical divider system

* Horizontal sync separator

The horizontal sync separator is supplied from the CVBS/Y inputs (chosen video source). For

horizontal synchronization the sync separator slices in the middle of the sync pulse and the slicing

level is independent of the sync pulse amplitude. For the vertical synchronization the sync pulse is

sliced at a level of about 30% (closer to the black level). This ensures optimal output signals for a

stable horizontal and vertical deflection under various video input conditions.

The top sync level is clamped at the CVBS input. The black level is stored internally.

* Horizontal oscillator and calibration system

The horizontal oscillator requires no external components and is fully integrated. The adjustment for

nominal frequency is derived automatically by a calibration circuit.

The oscillator generates a sawtooth signal with double horizontal frequency. This sawtooth signal is

used to derive several other gating and timing signals. After calibration the horizontal oscillator is

controlled by the PHI-1 loop for synchronization with the incoming video input signal.

The calibrator is responsible for the automatic adjustment of the horizontal oscillator. One of the color

crystals is being used as reference. For that reason a correct crystal selection by XA,XB (Xtal

selection) is very important during power-on. Calibration occurs during the vertical retrace period and

only under following conditions:

- At power-on/ initialization

- After power dip (shutdown detection), re-initialization is required.

- After loss of synchronization (e.g. after channel switching)

* PHI-1 detector

The PHI-1 detector is a PLL circuit that synchronizes the horizontal oscillator with the incoming video

signal. The PLL compares the output of the H-sync separator with the horizontal oscillator. The PLL

output current is converted to a voltage by means of the external loop filter. This voltage controls the

horizontal oscillator. The loop filter is connected externally so the time constant can be defined

according to the customer requirements. Because the static loop gain is very high there will be no

phase shift when switching between input signals with different line.

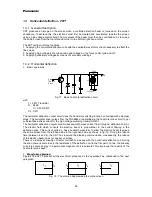

* PHI-2 detector and sandcastle

As described, the Horizontal PLL (PHI-1 loop) synchronizes the horizontal oscillator with the incoming

video signal. The PHI-2 loop provides a stable picture position on screen.

This is necessary because due to beam current variations the storage time of the line transistor varies

and, due to that, the picture position on screen.

The PHI-2 detector compares the horizontal oscillator signal (reference) with the horizontal flyback

input pulse, pin 41. This flyback pulse is related to the horizontal deflection.

The PHI-2 circuit shifts the horizontal drive, pin 40, such that the picture position on screen is constant.

The flyback input pin 41 is combined with the sandcastle output. This combined function provides a

three level sandcastle signal and is available starting with the highest level: burstkey, line blanking (=

flyback pulse) and vertical blanking.

The phase of the video signal with respect to the deflection current can be adapted by I²C bus HS

(horizontal shift, shift picture left/right).

The PHI-2 loop filter is a first order filter. The capacitor is connected externally on pin 42.