GB310 Service Manual

1

PANTECH

4.2.5 Offset PLL

4.2.5.1 An Overview of Offset PLL

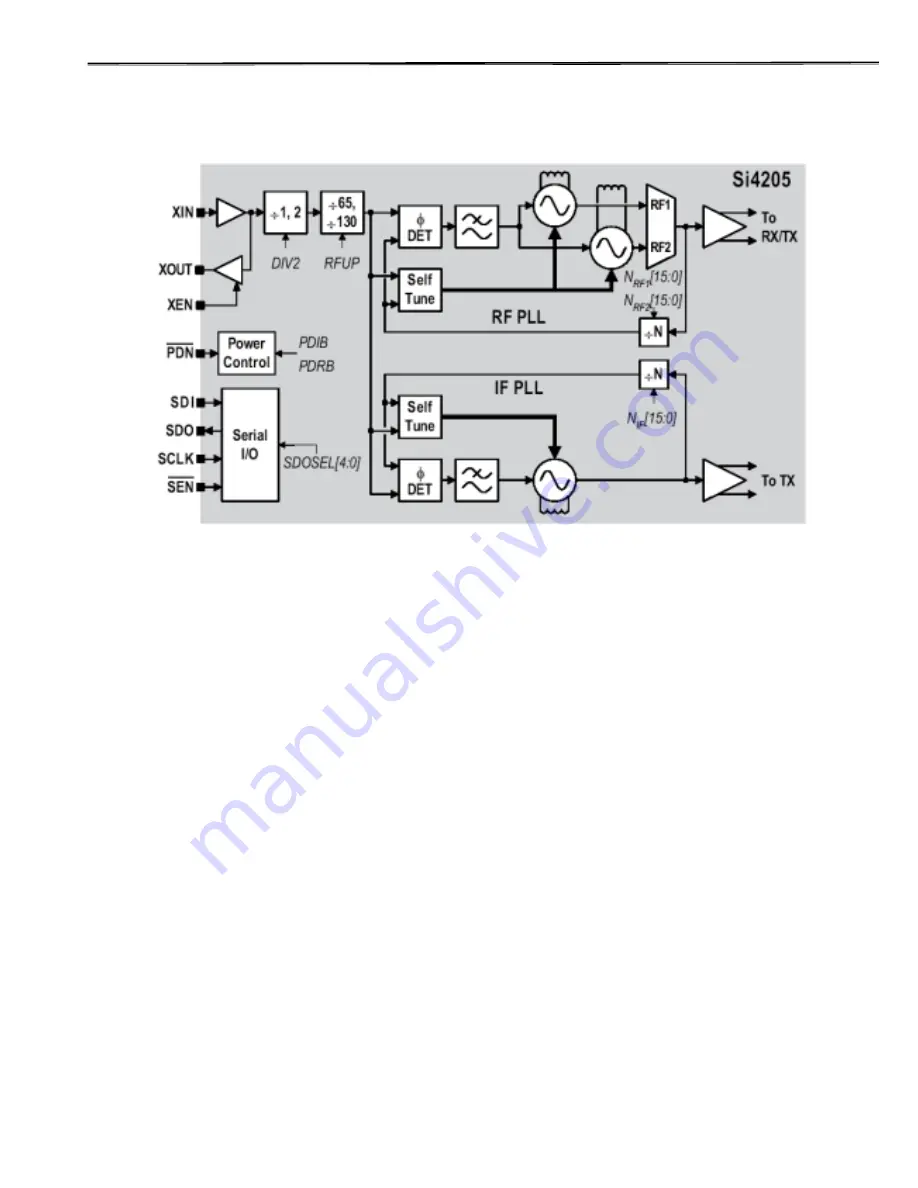

Fig.4-10. Si4205 Frequency Synthesizer Block Diagram

The Aero

I

transceiver integrates two complete PLLs including VCOs, varactors, resonators, loop

filters, reference and VCO dividers, and phase detectors. The RF PLL uses two multiplexed VCOs.

The RF1 VCO is used for receive mode, and the RF2 VCO is used for transmit mode. The IF PLL is

used only during transmit mode. All VCO tuning inductors are also integrated.

The IF and RF output frequencies are set by programming the N-Divider registers, NRF1, NRF2

and NIF. Programming the N-Divider register for either RF1 or RF2 automatically selects the proper

VCO. The output frequency of each PLL is as follows:

fOUT

=

N

×

f

φ

The DIV2 bit in register 31h controls a programmable divider at the XIN pin to allow either a 13 or 26

MHz reference frequency. For receive mode, the RF1 PLL phase detector update rate (f

φ

) should

be programmed f

φ

= 100 kHz for PCS 1900 bands, and f

φ

= 200 kHz for GSM 850 bands. For

transmit mode, the RF2 and IF PLL phase detector update rates are always f

φ

=200 kHz.