GRL-PCIE5-CEM-RXA User Guide and MOI

Rev7.0

© Granite River Labs 2022 Version 7.0, June 2022. Updated 06.29.2022

Page 83 of 123

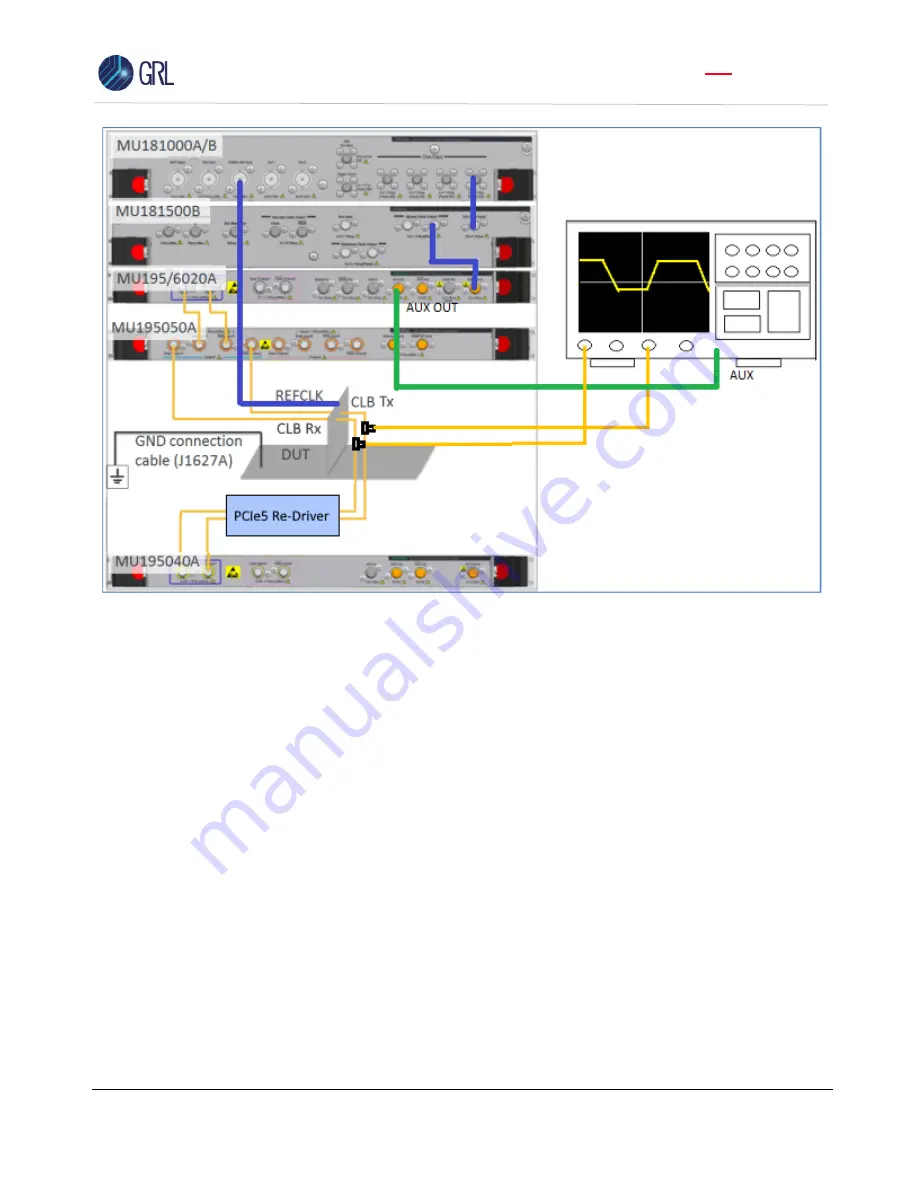

F

IGURE

54.

C

ONNECTION

D

IAGRAM FOR

PCI

E

G

EN

5

S

YSTEM

B

OARD

DUT

T

X

L

INK

EQ

R

ESPONSE

T

EST

Note

: Before starting the System Board DUT Tx Link EQ Response Test, make sure to perform

optimization of the Return Path (DUT Tx to BERT error detector). Refer to Appendix B or C for details.

1.

Using a SMA-SMA short cable, connect the MU181000A/B clock output to the MU181500B Ext

clock input.

2.

Using a SMA-SMA short cable, connect the MU181500B jittered clock output to the

MU195020A/MU196020A Ext clock input.

3.

Using coaxial cables, connect the MU195020A/MU196020A data outputs to the MU195050A

data inputs.

4.

Using coaxial cables, connect the MU195050A data outputs to Rx Lane 0 of the CLB.

5.

Using a BNC cable, connect the CLB 100 MHz clock output from the system board DUT to the

100 MHz reference clock input on the MU181000A/B.

6.

Using a SMA cable, connect a MU195020A/MU196020A Aux Out connector to an Aux input on

the oscilloscope.

Note the other unused MU195020A/MU196020A Aux Out connector must be

terminated with the J1632A coaxial terminator due to differential signal output (not shown in

above setup).

7.

Using coaxial cables, connect the CLB Tx Lane 0 to any of the pick-off tee input ports.