GRL-PCIE5-CEM-RXA User Guide and MOI

Rev7.0

© Granite River Labs 2022 Version 7.0, June 2022. Updated 06.29.2022

Page 91 of 123

8.3

Perform Rx Link EQ Test

This section describes how to set up the DUT for loopback testing to measure the Bit Error Rate

(BER) using the link equalization test method.

To perform link training loopback tests, the DUT attached to a test fixture will basically receive

data signals from a stress signal generator which is also connected to reference clock with the

DUT fixture. After data is processed, the signals will be sent back through the test fixture to the

stress signal generator for error detection. To enable this loopback mode, the error detector on

the stress signal generator will run link training procedure on the DUT. When the DUT enters

loopback state, the error detector will proceed to measure BER of the loopback signals.

Note:

Refer to Section 5.5 to set up the DUT for link equalization testing to verify initially that the

DUT is ready for link training and loopback.

8.3.1

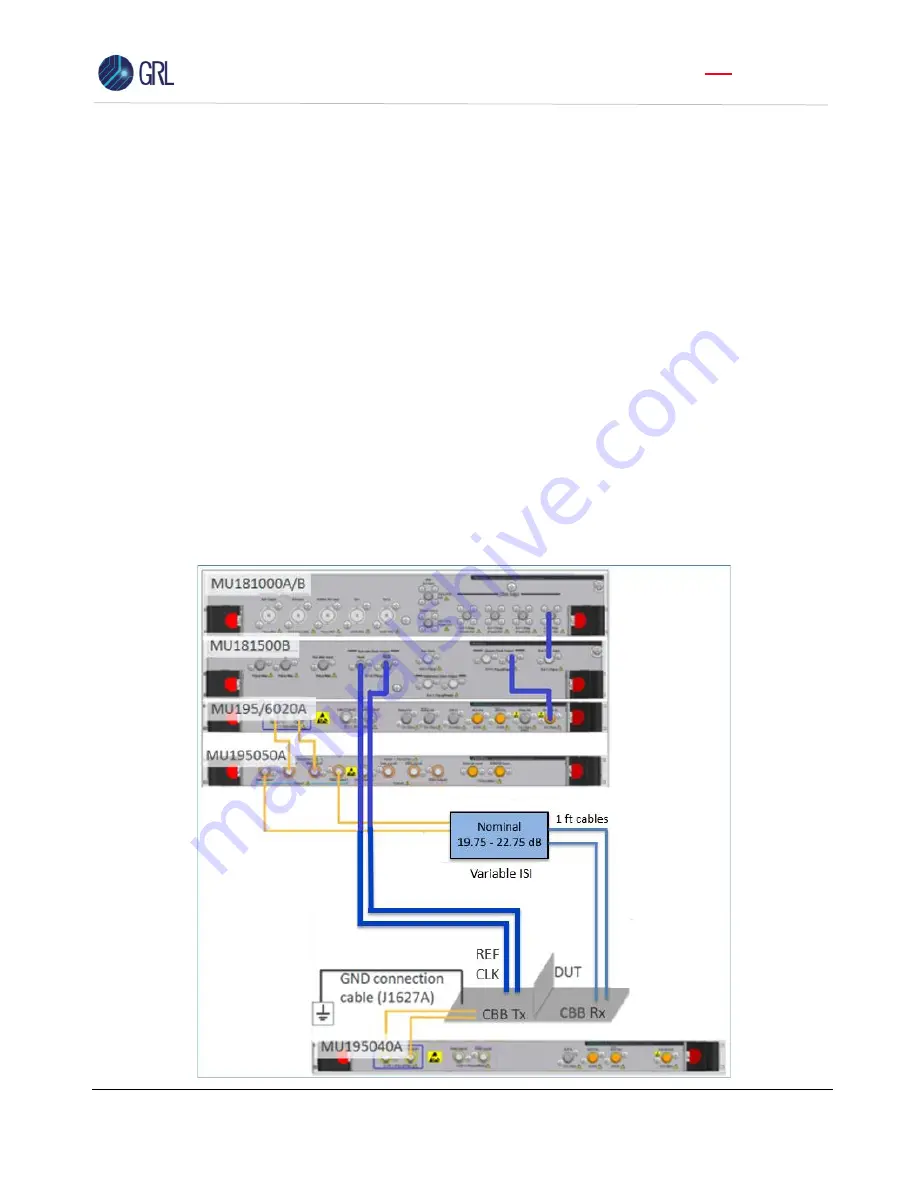

Equipment Setup for Add-in Card DUT Loopback Test

The following connection diagram shows the physical setup to enable loopback to perform link

training for the PCIe Gen 5 add-in card DUT. This setup is using the MP1900A BERT that includes

the MU195040A SI Error Detector module and a compliant CBB test fixture for the DUT.

Note

: Use logical Lane 0 for the following test setup.