GRL-PCIE5-CEM-RXA User Guide and MOI

Rev7.0

© Granite River Labs 2022 Version 7.0, June 2022. Updated 06.29.2022

Page 94 of 123

5.

Using 1 ft cables, connect between both the CLB Rx Lane 0 and Variable ISI.

6.

Using a BNC cable, connect the CLB 100 MHz clock output from the system board DUT to the

100 MHz reference clock input on the MU181000A/B.

7.

Using coaxial cables, connect the CLB Tx Lane 0 to the PCIe5 Re-Driver and then to the

MU195040A data inputs for loopback error detection.

8.

Using the J1627A GND connection cable, connect the CLB to ground.

8.3.3

Link Training Initialization and Testing

The Anritsu MX183000A High-Speed Serial Data test software is used with the MX190000A test

application on the MP1900A BERT to perform link training.

1.

Enable all calibrated stresses on the BERT.

2.

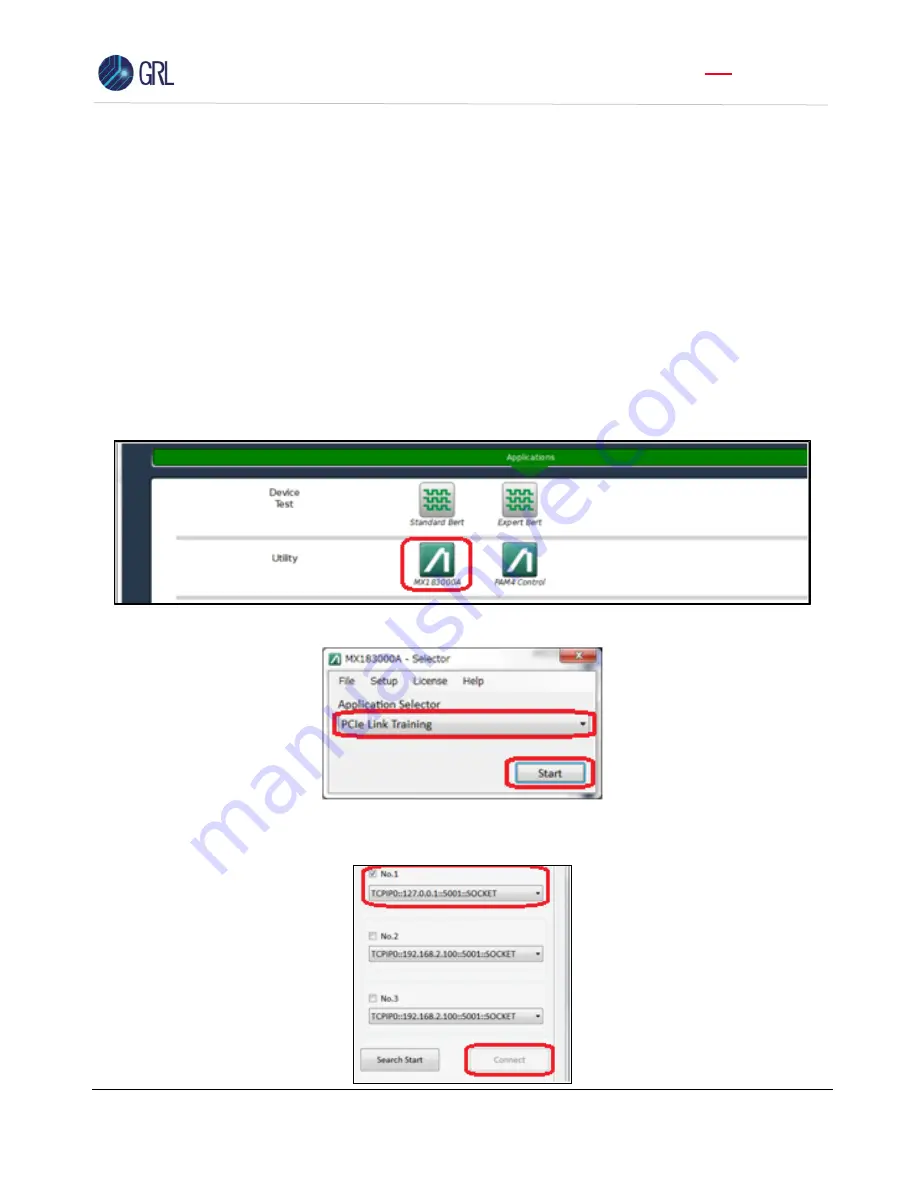

On the BERT’s Applications screen, select the MX183000A

Utility application.

3.

In the MX183000A - Selector pop-

up, select ‘PCIe Link Training’ and then ‘Start’.

4.

In the next window, select the network address of the MX190000A BERT application followed

by ‘Connect’ to link up with the MX190000A.