58

L9.1A

/78

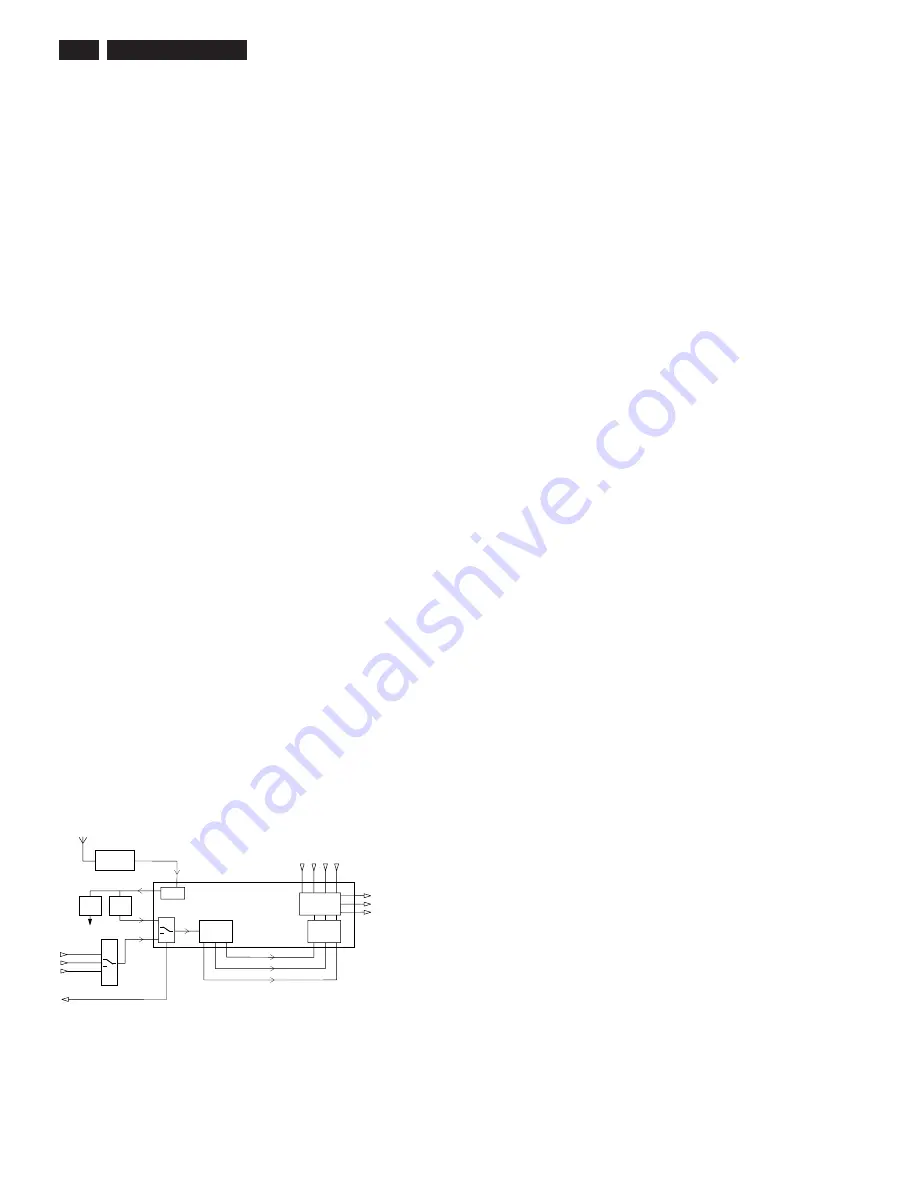

Figura 9-6: "Caminho de vídeo"

YC/CVBS EXT

YC/CVBS EXT

CVBS + SIF

R

G

B

TDA884X

SWITCH

TUNER

SOUND

TRAP

IF

CVBS_INT

SOUND

BPF

SIF

(to sound proc..)

CVBS_EXT

CVBS_MON

IF

48/49

25

21

32

38

6

13

17

30

29

28

27

31

19

20

24

23

26

CHROMA

PROCESSING

MATRIX

RGB

PROCESSING

+ SWITCH

YC/CVBS EXT

R

G

B

FBL

OSD/TXT/SCART

TO CRT

Y

U

V

TDA 8844/8845

Figura 9-6 “Caminho de vídeo”

9.6.2 Seleção CVBS/Y/C

Os chaveadores de entrada são utilizados para seleção do sinal

de entrada.

Três sinais de entrada podem ser selecionados:

•

Pino 13: entrada do CVBS terrestre.

•

Pino 17: entrada externa AV1.

e um estágio de ganho para ambos os formatos de modulação de

vídeo negativos e positivos, assim a amplitude de vídeo e o nível

DC corretos estão sempre presentes no pino 6 qualquer que seja

o sinal de entrada.

9.5.8 AGC de FI de Vídeo

Um sistema de AGC controla o ganho do amplificador de FI de vídeo

de forma que a amplitude de saída de vídeo é constante. O sinal vídeo

demodulado é fornecido, via filtro passa baixa interno ao IC para um

detector AGC. Um desacoplador externo ao AGC é fornecida pelo

capacitor 2201 no pino 53. A tensão detetora do AGC controla o estágio

de amplificação da FI.

9.5.9 O AGC do Tuner

O AGC do Tuner existe para reduzir o ganho do tuner e assim o sinal de

saída do tuner quando recebendo um sinal do RF forte. O AGC do tuner

começa trabalhando quando a entrada de FI de vídeo alcança um

certo nível de entrada. Este nível pode ser ajustado via o barramento

do IIC. O sinal de AGC do tuner é aplicado ao tuner via coletor aberto

do pino de saída 54 do BIMOS.

9.5.10 AFC

A informação de saída do AFC existe para procura de sintonia. O saída

do AFC está disponível via o barramento I2C(sinais AFA e AFB).

Para propósitos de ajuste ele é exibido no sub-menu TUNER do SAM

(Veja capítulo 8).

9.6 Processamento do Sinal de Vídeo (veja diagrama de circuito

A6)

9.6.1 Introdução:

O processamento do sinal de vídeo o pode ser dividido nas seguintes

partes:

•

Seleção de entrada CVBS/Y/C

•

Processamento dos sinais de Luminancia e chroma

•

Demodulação PAL/NTSC e SECAM / sistema automático de

gerenciamento

•

Procesamento YUV/RGB / aumento de preto

•

Segunda inserção RGB

•

Processamento RGB

•

Loop de calibração da corrente de preto

•

Limitador de corrente de feixe

Os circuitos de processamento citados acima são integrados ao

processador do TV (partes B e C). Os componentes periféricos são

adaptações da aplicação selecionada. O barramento I2C é utilizado

para definir e controlar os sinais.

•

Pin10/11: entrada externa AV2-Y, CVBS/C.

Quando pino 11 está no modo de entrada de CVBS então pino 10

não é utilizado.

Quando pino 11 está no modo de entrada Y/C então ambos os pinos são

utilizados e o filtro do sinal de Chroma no caminho de Y é desligado.

9.6.3 Processamento do Sinal de Chroma e Luminância

Uma vez que a fonte de sinal foi selecionada, a calibração do filtro de

Chroma é feita. A frequência do burst recebido da sub-portadora de

cor é utilizada para a calibração. Correspondentemente, o filtro passa a

faixa de chroma para processamento PAL/NTSC ou o filtro cloche

para processamento SECAM são ligados. Os pinos 34, 35 tem os

cristais conectados a eles. Esses cristais são utilizados para multi-

propósito de calibração do burst da sub-portadora. O sinal de luminância

selecionado é então fornecido aos circuitos de processamento de

sincronismo Horizontal e Vertical e para os circuitos de processamento

de luminância. No bloco de processamento da Luminância, o sinal do

luminancia é aplicado à armadilha do CHROMA.

Esta armadilha é ligada ou desligada conforme a detecção do burst de

cor no circuito de calibração de chroma. Antes do sinal do luminância

ser aplicado ao pino 28 do PROCESSADOR do TV o sinal é aplicado

a um circuito de pico e núcleo. Nestes circuitos o detalhe e o nivel

de ruído do sinal pode ser alterado via o controle remoto (menu

controle do usuário).

9.6.4 Demodulação PAL, NTSC e SECAM via o sistema automático

de gerenciamento

O circuito decoder de cor detecta se o sinal é PAL ou sinal NTSC. O

resultado é informado ao sistema automático de gerenciamento. A linha

de atraso da base-banda é ativada quando um sinal PAL ou SECAM

é detectado. Para o padrão de cor SECAM uma tensão de referência é

gerada no pino 16 do processador do TV.

Conectado ao pino 9 do processador do TV, está o circuito desacoplador

de intervalo de banda, que consiste de (2214,2215). O circuito de

intervalo de banda fornece uma tensão de referência muito estável e

independente de temperatura. Isto assegura uma performance ótima do

processador do TV e é utilizado por quase todos os blocos funcionais

internos ao processador. O sinal Y e as saídas do demodulator R-y

e B-y estão presentes nos pinos 28, 29, 30 do processdor do TV. O

sistema automático identifica os padrões de cor PAL, NTSC e SECAM é

controlado via o barramento IIC. Conectado ao pino 36 do processador

do TV está o Filtro Loop para o detector de fase.

O filtro escolhido fornece uma resposta transitória ótima, que assegura

uma ótima largura de banda e tempo de aquisição de cor.

9.6.5 Processamento YUV / RGB / Aumento de preto

Os sinais Y , R-y e B-y presentes nos pinos 27, 31, 32 do processador do

TV são utilizados como sinais de entrada para a seção de decodificação

de cor do BiMOS (IC7520-C). O processador de YUV habilita o controle

de saturação de cores e também converte os sinais Y, B-y e R-y no

formato dos sinais R, G, B via o circuito matriz de cor. O circuito de

aumento preto, estágio inicial do circuito matriz, extende o nível do sinal

de cinza ao nível de preto atual. A quantia de extensão depende da

diferença entre nível preto atual e a parte mais escura do nível do sinal

de vídeo que está entrando. Este recurso é totalmente integrado. O

usuário pode ligar ou desligar este circuito usando a opção de Contrast

Plus no menu do usuário.

9.6.6 Segunda inserção de RGB

Os pinos 23, 24, 25 são utilizados como as entradas da segundo

inserção de sinais R, G, B. Pino 26 do processador do TV é a entrada

do sinal de controle de inserção que é chamado “FBL”. Quando o nível

do sinal FBL torna-se mais alto que 0.9V (mas menos que 3V), os

sinais R,G, B nos pinos 23,24,25 são inseridos na imagem usando os

interruptores internos incorporados no processador do TV.

Esta segunda possibilidade de inserção é utilizada para inserção do

OSD sinais TXT ou sinais R. G. B do soquete CINCH.

Summary of Contents for 21PT836A/78

Page 23: ...23 L9 1A 78 6 Localização de Defeitos Esquemas e Resumo ...

Page 24: ...24 L9 1A 78 6 Localização de Defeitos Esquemas e Resumo ...

Page 34: ...34 L9 1A 78 7 Esquemas Elétricos e Guias de Placas ...

Page 36: ...36 L9 1A 78 7 Esquemas Elétricos e Guias de Placas ...

Page 44: ...44 L9 1A 78 7 Esquemas Elétricos e Guias de Placas ...

Page 46: ...46 L9 1A 78 Painel AV Lateral Fone de Ouvido CL 06532025_031 eps 030400 ...