EN 116

Q549.2E LA

10.

Circuit Diagrams and PWB Layouts

2009-May-08

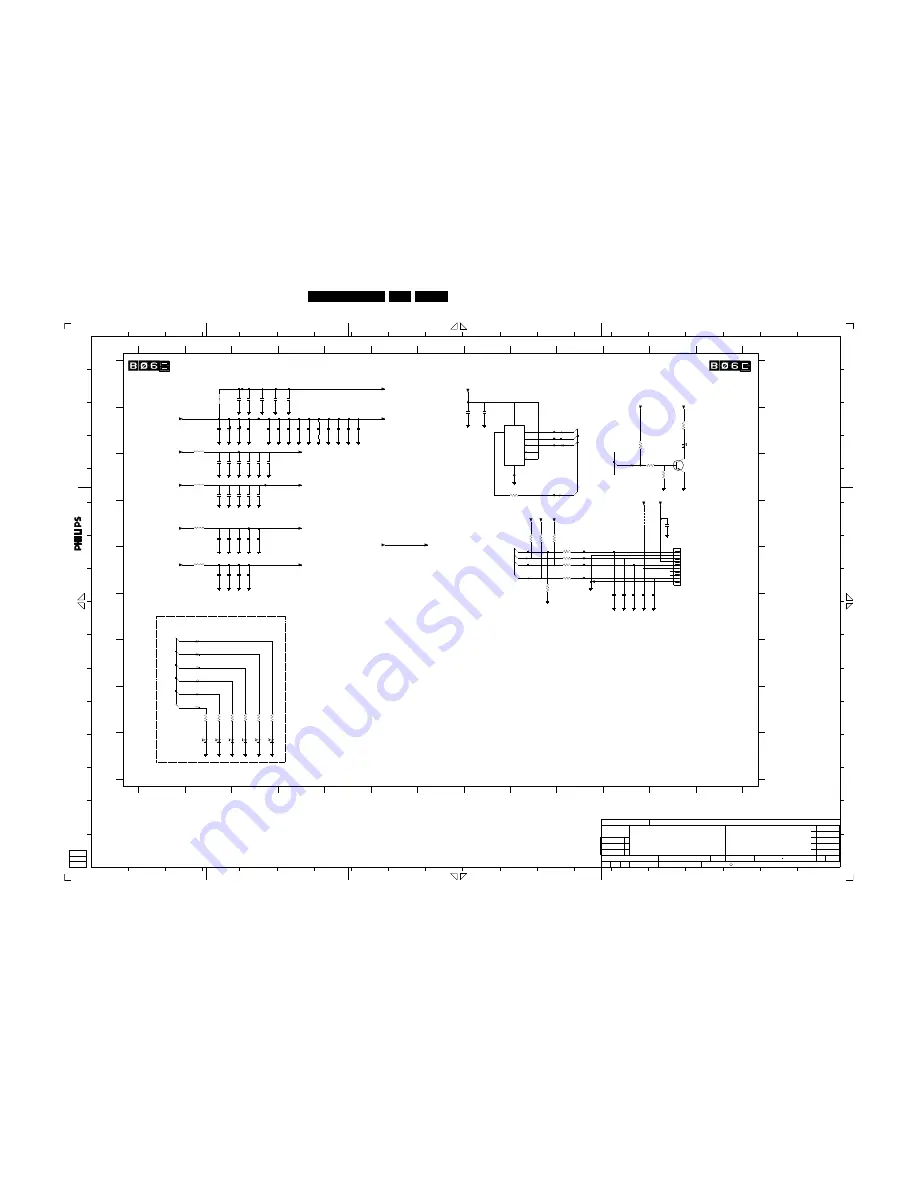

SSB: FPGA WOW - Power & Control

C

D

C

S

W

HOLD

VSS

Q

VCC

6FH3 I3

6FH0 I2

15

FOR DEBUG

L

D

6FH6 I3

6FH1 I2

6FH2 I2

H

9

8

All rights reserved. Reproduction in whole or in parts

2FHW D3

2FHZ D3

2FJ0 D3

4

6FH7 I3

10

5

C

2

20

12

2FJ1 D2

2FJ2 D2

2FJ3 F11

17

2FJ4 F11

18

FFH6 E10

FOR

16

P

O

N

16

17

15

E

B

10

2FH9 E3

DEBUG

6

11

8

2FHA A3

2FHB C3

2FHC B3

2FHD B4

6FH8 B12

19

13

7

J

4

A

11

3

7

19

H

FPGA WOW - POWER & CONTROL

O

2FH1 B5

8

2FH3 A3

9

6

7

8

2FJ5 F11

2FJ6 F11

B

FFH7 E10

FFH8 E10

FFH9 E10

D

FFHM B9

6

FFHP B9

FFHR C9

FFHS C9

IFH4 A7

5FH4 E2

P

13

1

5

2

1

1

1

0

1

9

7

5

4

3

2FHE B4

2FHF B4

7FH0 B8

7FH2 C12

9FH0 D11

CFH1 D6

FFH1 B3

FFH2 B3

FFH3 C3

G

FFH5 E10

A

I

6

F

G

2FH8 E3

I

1F00 E12

2FH0 B5

M

2FH2 A3

2FH4 A3

2FH5 A4

2FH6 E2

2

9

2FJ8 C2

2FJ7 D12

H

3FHB-4 E10

3FHG C9

FFHA E3

3FHK C12

FFHN B9

3FHM B12

5FH0 A2

5FH1 B2

FFHT C11

5FH3 D2

N

F

14

K

18

owner.

B

F

3FH2 H2

3FH3 H3

3FH6 H3

3FH7 H3

3FH8 D9

3FH9-1 D9

2FJA C3

CFH0 B2

2FHP C3

FFH0 A3

3FH9-2 D9

3FH9-3 E9

3FHB-1 E10

FFH4 D3

3FHB-3 E10

I

E

2FHJ B5

2FH7 E2

13

14

J

K

1

20

10

11

D

E

F

2FHG B4

H

3FHJ C12

2FJJ B8

2FJK B7

2FJP B3

3FH0 H2

3FH1 H2

1

2FHS C3

5FH2 C2

G

C

L

is prohibited without the written consent of the copyright

G

3

2

E

2FHL B2

2FHM B2

2FHN C2

2FHR C3

13

2FHT B3

2FHV C3

5

4

3

1

2FHH B4

3FHL B11

2FHK B5

3FHB-2 E10

C

D

A

B

12

I

M

2

2FJ9 C2

12

2FJB C3

2FJC C3

2FJD F12

A

C

100p

2FJ3

CFH1

+2V5

RES

5FH3

30R

10K

+1V8-PNX85XX

2FJ1

3FHL

100n

2FHK

10n

+2V5

+2V5

2FHW

100n

3FH9-1

1K0

2FJB

100n

FFH8

30R

5FH2

1K0

3FH9-3

2FHT

330u

6.3V

RES

5FH0

30R

FFH4

2FH2

100n

100n

2FJA

3FHB-4

100R

4

5

FFH1

2FJP

4u7

+2V5

30R

5FH1

100R

3FHB-2

2

7

9FH0

RES

+1V8-PNX5100

3FHK

100K

2FH3

100n

2FHJ

10n

FFHP

+2V5in-FPGA

10n

2FH1

2

3

4

5

6

7

8

9

5-147279-2

1F00

1

10

3FH2

470R

FFHR

470R

3FH1

+3V3

FFH7

100n

2FH7

FFH2

+2V5

100R

3FHB-1

1

8

470R

3FH3

RES

2FJ4

100p

LTST-C190KGKT

6FH2

1K0

3FHM

100n

2FHF

10n

2FH4

4u7

FFHN

+3V3-FPGA

2FHN

+1V2-FPGA

3FH0

470R

2FHL

100u

4V

3

6

3FHB-3

100R

100n

2FHR

2FJ6

10n

FFH6

RES

FFH9

2FH0

10n

6FH3

LTST-C190KGKT

+1V2-PNX85XX

RES

1

00p

2FJD

100n

2FJK

FFHT

6FH8

SML-310

+2V5in-FPGA

+3V3

BC847BW

7FH2

2FHE

10n

47R

3FHG

130

+2V5out-FPGA

ROYAL PHILIPS ELECTRONICS N.V. 2007

2007-12-04

5

8

SETNAME

CHN

CLASS_NO

SUPERS.

2

NAME

DATE

CHECK

8204 000 8933

TV543 R2 LDIPNX

FPGA WOW - POWER & CONTROL

A2

3

2008-10-10

Maelegheer Ingrid

2008-11-21

FFHM

2FJ0

100n

100n

2FJJ

10n

RES

2FHG

2FH5

100n

100n

2FHV

RES

100n

2FJC

2FJ7

10n

4u7

2FHA

5

7

2

1

8

4

3

M25P16

7FH0

16M

Φ

FLASH

6

100n

2FHB

FFHA

+2V5

+3V3

IFH4

2FJ8

4u7

2FJ9

100n

2FHP

100n

FFHS

+1V2-PLL

2FH6

100n

100n

2FHS

100p

2FJ5

6FH7

LTST-C190KGKT

RES

470R

3FH7

RES

3FHJ

100K

2FHD

10n

+2V5-PLL

+2V5

100n

2FH9

2FH8

100n

1K0

3FH9-4

3FH6

470R

100n

2FHZ

3FH8

1K0

RES

FFH5

10n

2FHC

+2V5

2FHM

4u7

CFH0

10n

2FHH

FFH0

LTST-C190KGKT

6FH6

LTST-C190KGKT

6FH0

6FH1

LTST-C190KGKT

4u7

2FJ2

FFH3

30R

5FH4

nCSO

ASDO

DATA0

CON26

CON27

DCLK

CON23

CONF-DONE

CON20

CON21

CON22

TCK

TDI

TDO

TMS

1

83

10_5

3

1_090

3

0

3

.ep

s

090

3

0

3