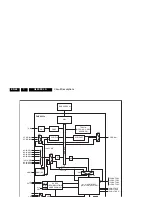

Circuit Descriptions

EN 46

Q549.2E LA

7.

2009-May-08

Figure 7-7 PNX8543 functional diagram

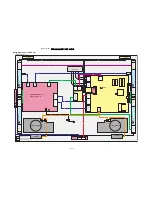

7.5.1

Video Subsystem

Refer to

Figure 7-8

for the main video interfaces for the

PNX8543 and the video signal flow between blocks and

memory.

1

8

440_202_090226.ep

s

090226

T

S

o

u

t/in for

T

S

in from

CVB

S

, Y/C,

LVD

S

for

a

n

a

log CVB

S

a

n

a

log

au

dio

I

2

S

D

ua

l

S

PDIF

Low-IF

SS

IF, LR

D

ua

l HDMI

S

PDIF

CI/CA

MPEG

PRIMARY

LVD

S

VIDEO

S

ECONDARY

MEMORY

VIDEO

3

D COMB

DIGITAL IF

AUDIO DEMOD

AUDIO IN

HDMI

S

CALER,

AUDIO D

S

P

AUDIO DAC

S

AUDIO OUT

3

00 MHz

3

00 MHz

I

2

C

PWM

GPIO

IR

ADC

UART

I

2

C

GPIO

Fl

as

h

S

Y

S

TEM

U

S

B 2.0 CA

PNX

8

54

3

x

DV INPUT

DV-ITU-656

AV-PIP

S

PI

MPEG/H.264

I

2

S

RECEIVER

(

8

051)

CONTROLLER

AND DECODE

DECODER

ch

a

nnel decoder

PCMCIA

RGB

PROCE

SS

OR

S

Y

S

TEM

CONTROLLER

DECODER

VIDEO

CPU

MIP

S3

2 4KEc

0

1

x

2

2

x

AV-D

S

P

REDUCTION

AND NOI

S

E

DE-INTERLACE

OUTPUT

VIDEO

S

UB-PICTURE

ENCODER

OUTPUT

VIDEO

ch

a

nnel)

(

s

ingle or d

ua

l

fl

a

t p

a

nel di

s

pl

a

y

DRAWING

ENGINE

DMA BLOCK

PCI 2.2