IC Data Sheets

EN 56

Q549.2E LA

8.

2009-May-08

8.4

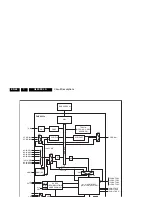

Diagram

SSB: Ethernet

B05A, PNX5120 (IC7C00)

Figure 8-4 Internal block diagram and pin configuration

1

8

560_

3

00_09040

3

.ep

s

09040

3

Pin Confi

g

uration

Block Dia

g

ram

PNX51xx

Tr

a

n

s

p

a

rent top view

2

4

6

8

10 12

1

3

14

15 17

16

19

1

8

20

21 2

3

22 24

25

26

1

3

5

7

9 11

ba

ll A1

index

a

re

a

AB

AD

AA

AC

Y

W

V

U

R

N

T

P

M

L

K

J

H

F

D

G

E

C

B

A

AF

AE

LVD

S

RX 1

UIP L

3

K7

TM

3

27x 1

CONTROLLER

PCI/XIO

I2C-DMA

UART

CPIPE L

3

K7

LVD

S

TX 2

UART

PNX51xx

I2C

I2C

TM

3

27x 2

TM

3

27x

3

LVD

S

TX

3

LVD

S

TX 1

LVD

S

TX 4

GFX

16 X GPIO

GIC

3

EJTAG

CLOCK

CAB

Video

LVD

S

RX 2

AUDIO IN

AUDIO OUT

GIC 1

GIC 2

MEMORY

Video