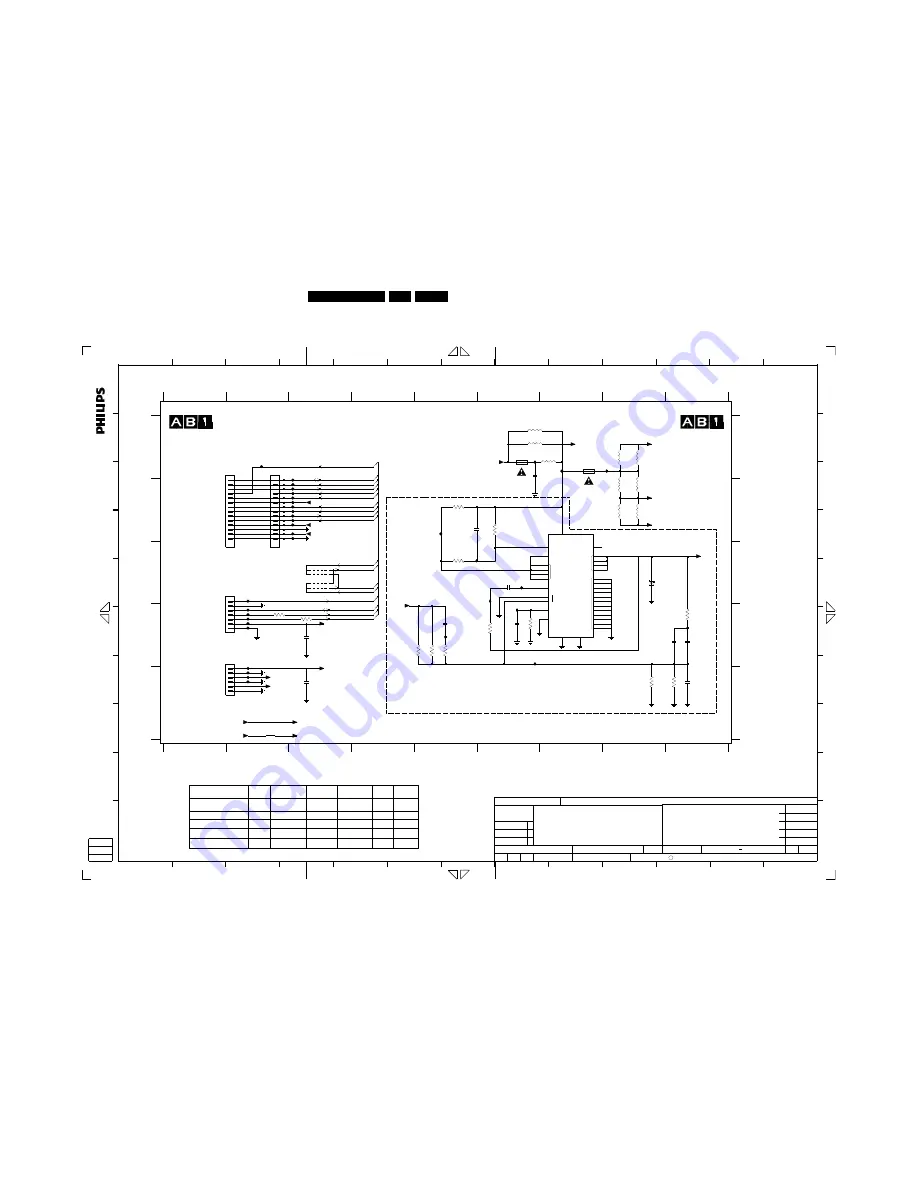

Circuit Diagrams and PWB Layouts

EN 67

Q549.2E LA

10.

2009-May-08

10. Circuit Diagrams and PWB Layouts

Interface Ambilight: Int Single DC-DC

C

VCC

GND

GND_H

S

S

WI_EMIT

S

WI_COL

VFB

LVI_OUT

VIA

LPK_

S

EN

S

E

DRV_COL

BOOT_IN

2

1

TIM_CAP

NC

o

u

t

9

in

E

in

F

o

u

t

1M

8

5

2

9

I

3

104

3

2

8

5

83

51

1

A

o

u

t

o

u

t

1

3

in

3

104

3

2

8

5

83

71

o

u

t

3

109 D2

o

u

t

G

1

3

3

110 D

3

7

C

D

o

u

t

510

3

/5104

3

104

3

2

8

5

83

41

12V

2107 E9

210

8

D

3

2109 E

3

3

100 B5

owner.

7

E

3

105 D5

3

106 D5

3

107 D5

3

10

8

E9

12V

12

16V

11

6

c002 E2

8

5

3

4

S

TUFFING DIVER

S

ITIE

S

FOR DC/DC INTERFACE AMBI 2K9

F122 E2

F12

3

E2

F124 E2

F125 B

3

F126 A2

I100 A6

I101 C6

I102 C6

I10

3

C6

B

I109 A

8

c001 E2

1101

H

INT

S

INGLE DC-DC

o

u

t

All right

s

re

s

erved. Reprod

u

ction in whole or in p

a

rt

s

2

24V

10

o

u

t

o

u

t

2102 C6

210

3

D6

o

u

t

F121 E2

F114 B5

F115 C2

3

101 C5

3

102 D6

3

10

3

D9

3

104 D6

F120 D2

I

3

8

1

2

3

4

5

6

7

8

9

1

2

5106 B

8

5107 A6

5

6

7

in

6

12

J

VLED2

I104 D9

I105 D5

I106 D7

I10

8

D6

C

D

E

A

B

C

D

E

1100 A6

1101 A7

1M59 C2

1M

8

4 A2

1M

8

5 A2

1M90 D2

2100 A6

2101 B5

F109 B

3

F110 B

3

2104 D5

2105 D9

2106 D9

4

3

1

16V

3

104

3

2

8

5

83

61

F116 D2

F117 D2

F11

8

D2

F119 D2

16V

6

3

V

C

RE

S

S

ee the

s

t

u

ffing diver

s

itie

s

t

ab

le in the c

as

e of component

s

m

a

rked with one

s

t

a

r (

*

)

i

s

prohi

b

ited witho

u

t the written con

s

ent of the copyright

H

G

3

111 E

8

3

112 B6

5100 A

8

5101 A

8

5102 A7

510

3

B

8

5104 B

8

5105 B

8

16V

510

8

A6

6100 C

8

7100 B7

5105/5106

in

B

DC/DC INTERFACE

8

D

9

A

B

10

J

11

9101 C

3

9102 C

3

910

3

C

3

9104 C

3

F101 B

3

F102 B

3

F10

3

B

3

F104 B

3

F105 B

3

F106 B

3

F107 A7

F10

8

B

3

F111 B

3

F112 B

3

F11

3

B

3

A

5

4

F

VLED1

12V

RE

S

+16V

F11

8

5101

3

0R

V

S

W

I10

8

F10

3

+

3

V

3

+24VF

F112

I100

+12V

RE

S

100R

3

109

4

5

6

7

17

3

5446-7

1M59

1

2

3

+24V

F107

(RE

S

)

910

3

I106

3

K

3

3

10

8

1

%

3

102

15K

2102

F101

2n2

F104

5106

3

0R

*

+16V

+16V

F122

9104

1

S

UPER

S

.

1

NAME

DATE

MGr

CHECK

3

104

3

1

3

6

3

25

AMBI 2K9

DC-DC INTERFACE

A

3

0

8

-0

8

-06

0

8

-06-19

0

8

-12-06

0

8

-10-2

3

0

8

-09-1

8

0

8

-0

8

-06

5

4

3

2

***

0

3

1

*

*

3

2

0

8

-10-2

3

Peter V

a

n Hove

0

8

-06-19

CT

ROYAL PHILIP

S

ELECTRONIC

S

N.V. 200

8

0

8

-06-06

********

1

3

S

ETNAME

CHN

CLA

SS

_NO

100n

2105

1M0

3

105

F115

I101

F12

3

F111

3

101

47R

1

2

3

4

5

6

17

3

5446-6

1M90

9102

F117

(RE

S

)

3

104

33

0R

F121

F120

+24V

220p

210

3

12K

3

107

F102

VLED2

*

F124

3

0R

5105

F126

+24V

c001

F10

8

F105

F109

3

0

3

1

21

22

2

3

24

25

26

27

2

8

10

11

12

1

3

1

3

17

16

20

29

5

1

8

19

5

1

4

2

6

7

8

9

NCP

3

16

3

BMNR2G

7100

Φ

14

VLED1

+

3

V

3

100n

2107

T

2.0A

1101

I109

*

3

0R

5107

RE

S

3

0R

510

8

RE

S

F110

1

%

33

K

3

106

3

0R

5100

RE

S

5

6

7

8

9

15

16

1

10

11

12

1

3

14

2

3

4

F11

3

502

38

2-1470

1M

8

4

100K

3

111

2100

220n

2101

10n

3

100

0R1

F114

RE

S

VLED2

210

8

100p

100R

3

112

VLED1

c002

2106

100n

1100

3

.0A

3

2V

T

10

u

5102

100p

2109

RE

S

9101

F116

+12V

3

110

100R

RE

S

F106

+24V

F125

I10

3

I105

9

15

16

I104

1

3

14

2

3

4

5

6

7

8

1M

8

5

502

38

2-1470

*

1

10

11

12

100n

2104

+16V

SS

24

6100

3

0R

5104

*

510

3

3

0R

*

3

10

3

3

K

3

F119

S

PI-LATCH2CONN

S

PI-LATCH1CONN

S

PI-LATCH2CONN

S

PI-LATCH1CONN

S

PI-LATCH2

S

PI-LATCH1

I102

CONTROL1

CONTROL2

S

DA

S

PI-CLOCK-BUF

S

PI-DATA-RETURN

S

PI-DATA-OUT

PWM-CLOCK-BUF

BLANK-BUF

EEPROM-C

S

TEMP-

S

EN

S

OR

PROG

S

CL

1

83

10_600_090

3

05

.ep

s

090

3

05