IC Data Sheets

8.

8.

IC Data Sheets

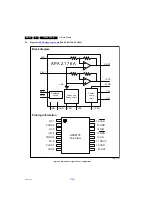

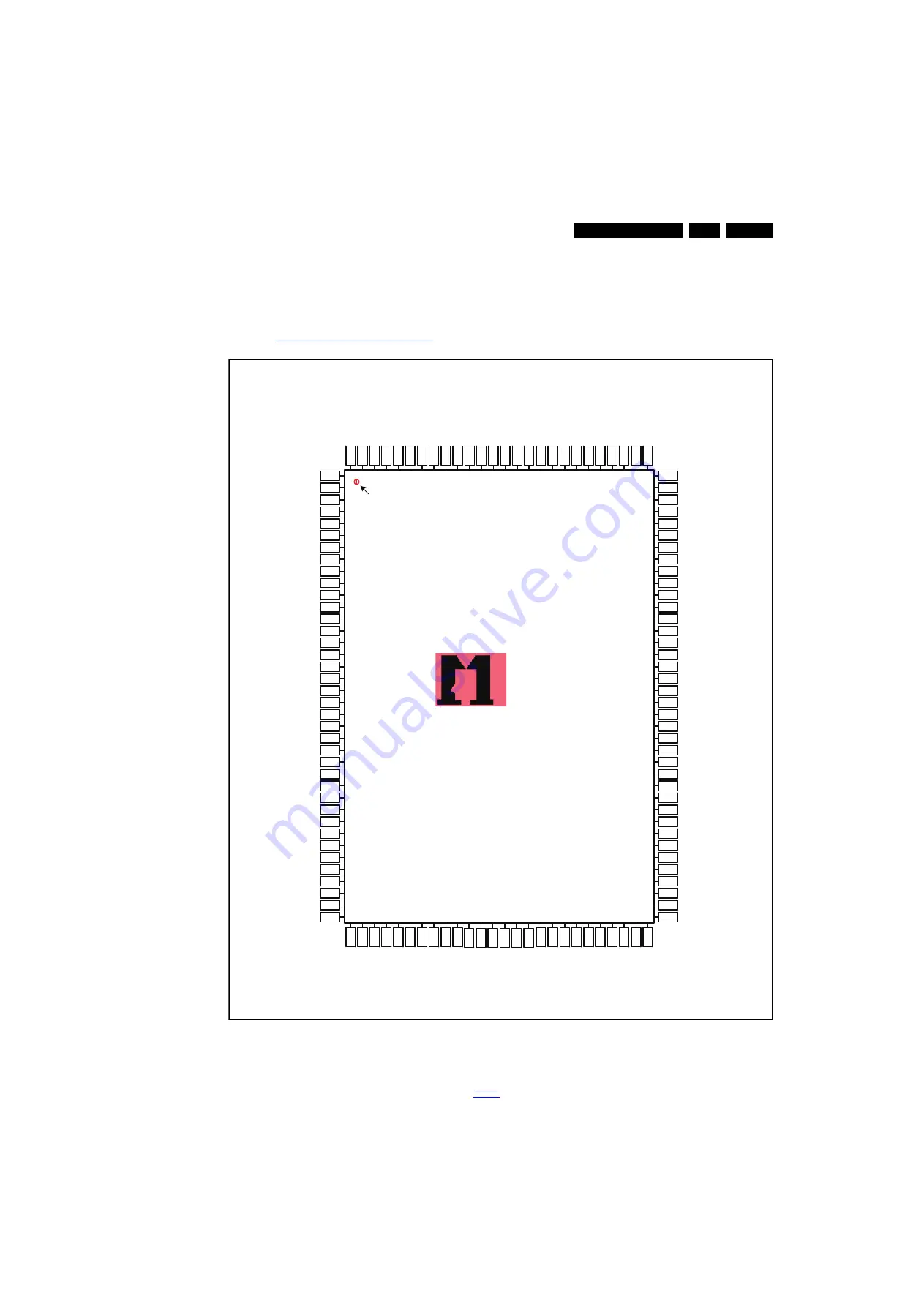

This chapter shows the internal block diagrams and pin

configurations of ICs that are drawn as “black boxes” in the

electrical diagrams (with the exception of “memory” and “logic”

ICs).

8.1

Diagram

Figure 8-1 pin configuration

19660_300.eps

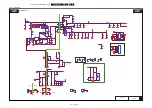

Pinning Information

Pin 1

RXACKN

1

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

36

37

38

3

9

40

67

66

65

6

3

62

61

60

59

5

8

57

56

55

4

8

47

46

45

44

4

3

42

41

64

81

80

79

78

77

76

75

74

73

72

71

70

69

68

102

101

100

99

98

97

95

94

93

92

91

90

89

88

87

86

85

84

83

82

10

4

10

3

12

6

12

5

12

4

12

0

11

9

11

8

12

2

12

1

11

0

10

9

10

8

10

7

10

6

10

5

11

2

11

1

12

3

11

7

11

6

11

5

11

4

11

3

12

8

12

7

96

AVDD_12

ARC

DDCDA_CK

RXA2P

DDCDA_DA

RXA2N

HSYNC0

RXA1P

RXA0P

RXA0N

RXACKP

RXA1N

AVDD_MOD

BIN0P

SOGIN0

GIN0M

GIN0P

RIN0P

VSYNC0

AVDD_ADC33

BIN1P

AUREFM

AVDD_AU33

CVBSOUT1

CVBS1

HSYNC1

CVBS0

RIN1P

VSYNC1

SOGIN1

GIN1M

GIN1P

LINEIN_L1

VCOM

AUVAG

LINEIN_R1

LINEIN_L3

LINE

IN_R

3

LIN

E

IN_L4

LINE

IN_R5

LINE

IN_R4

LINE

IN_L5

LINE

OUT

_

L

3

GN

D

VD

DIO

_

C

M

D

LIN

E

O

U

T

_

R

3

LINEO

U

T

_L0

TA

G

C

XIN

LIN

E

O

U

T

_

R

0

XO

UT

54

5

3

52

51

50

49

AV

D

D

_

D

M

P

L

L

A

V

DD

_REF

IP

IM

VDDC

LV

A

4

P

GP

IO[

5

6]

A

V

D

D

_PLL

GP

IO[

5

5]

LV

A

3

P

LV

A

4

M

LV

A

3

M

LVACKM

LVACKP

LVB3M

LVA1P

LVA1M

LVA0P

LVA2P

LVA2M

LVA0M

LVB4P

LVB4M

AVDD_MOD

LVB3P

AVDD_MOD

LVB2M

AVDD_MOD

PWM2

DP_P0

SDO

SDI

TS1_D[0]

LVB0M

VDDC

GPIO[65]

LVB1M

LVB0P

TS1_VLD

TS1_SYNC

LVB1P

DP_P1

DM_P1

TS1_CLK

DM_P0

CSZ

SCK

LVBCKP

LVB2P

LVBCKM

RXD0N

RXD0P

S

AR

2

IR

IN

PW

M

1

PWM

0

DDC

A_CK

VDDIO

_D

A

T

A

DDC

A_D

A

GN

D

S

AR

1

GND

RE

S

ET

CE

C

HO

T

P

LU

GD

RXDC

K

N

RXDC

K

P

GP

IO11

S

AR

0

RXD2P

HO

T

P

LU

GA

RXD1P

DDC

D

D_CK

RXD2N

RXD1N

DDC

D

D_D

A

MST6931XP

XXXXXXXX

XXXXX