9-5

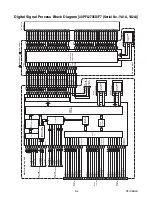

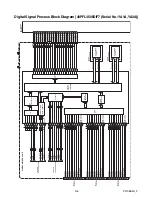

Digital Signal Process Block Diagram [40PFL3505D/F7 (Serial No.: YA1A, YA3A)]

PL10.5BLD_2

LVDS-D4O(+)

35

LVDS-D4O(-)

36

DIGIT

AL MAIN CB

A UNIT

IC3301

(DIGIT

AL SIGNAL PR

OCESS)

LCD MODULE

ASSEMBL

Y

CN3901

LVDS-D1E(+)

21

LVDS-D1E(-)

22

LVDS-D0E(+)

23

LVDS-D0E(-)

24

LVDS-D2E(+)

19

LVDS-D2E(-)

20

LVDS-D3E(+)

13

LVDS-D3E(-)

14

LVDS-D0O(+)

47

LVDS-D0O(-)

48

LVDS-D1O(+)

45

LVDS-D1O(-)

46

LVDS-D2O(+)

43

LVDS-D2O(-)

44

LVDS-D3O(+)

37

LVDS-D3O(-)

38

LVDS-ECLK(+)

16

LVDS-ECLK(-)

17

AD23

AD24

AE23

AF23

AF22

AE22

AD21

AD22

AF24

AE24

AF18

AE18

AD17

AD18

AE17

AF17

AF16

AE16

AD15

AD16

LVDS

TX

LVDS-D4E(+)

11

LVDS-D4E(-)

12

AE21

AF21

LVDS-OCLK(+)

40

LVDS-OCLK(-)

41

AE19

AF19

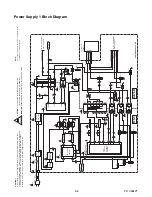

DIGIT

AL

SIGNAL

PR

OCESS

A/D

CONVER

TER

SW

V1

V2

U2

U1

U3

V3

Pr/S-C-IN

Pb-IN

CVBS/Y/S-Y

-IN

AA3

IF-A

GC

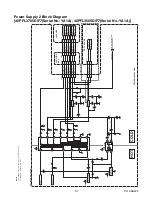

HDMI2-SCL

HDMI2-SD

A

HDMI-IN1

JK3803

D

A

T

A0(+)

D

A

T

A0(-)

D

A

T

A1(+)

D

A

T

A1(-)

D

A

T

A2(+)

D

A

T

A2(-)

HDMI-CLOCK

HDMI-D

A

T

A

7

9

4

6

1

3

10

12

15

16

CLOCK(+)

CLOCK(-)

DEMODULA

T

O

R

/MPEG DECODER

AF2

AF7

A

UDIO I/F

TO

A

U

D

IO

BLOCK DIA

GRAM

A

CLK

A

D

ATA

1

BCLK

LRCLK

A

D

ATA

0

SPDIF

AD14

AD9

AD12

AD10

AD11

A

C10

HDMI

I/F

D1

D2

C1

C2

B1

B2

A1

A2

DIF-OUT1

DIF-OUT2

IF-A

GC

T

O

VIDEO

BLOCK DIA

GRAM

AE2

M2

A

UDIO(R)

M1

A

UDIO(L)

VIDEO SIGNAL

AUDIO SIGNAL

HDMI-IN2

JK3801

D

A

T

A0(+)

D

A

T

A0(-)

D

A

T

A1(+)

D

A

T

A1(-)

D

A

T

A2(+)

D

A

T

A2(-)

HDMI-CLOCK

HDMI-D

A

T

A

7

9

4

6

1

3

10

12

15

16

CLOCK(+)

CLOCK(-)

HDMI-IN3

JK3802

D

A

T

A0(+)

D

A

T

A0(-)

D

A

T

A1(+)

D

A

T

A1(-)

D

A

T

A2(+)

D

A

T

A2(-)

HDMI-CLOCK

HDMI-D

A

T

A

7

9

4

6

1

3

10

12

15

16

CLOCK(+)

CLOCK(-)

B8

A8

C8

C9

A9

B9

B10

A10

B4

A4

C4

C5

A5

B5

B6

A6

B3

A3

HDMI0-SCL

HDMI0-SD

A

B11

A11

HDMI1-SCL

HDMI1-SD

A

B7

A7

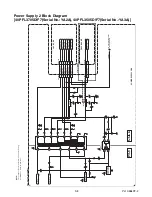

S0-DQ (0-15)

S0-A (0-12)

(DDR2 SDRAM)

IC3201

DDR2 SDRAM

( 512M bit )

S1-DQ (0-15)

S1-A (0-12)

(DDR2 SDRAM)

IC3202

DDR2 SDRAM

( 512M bit )

A

UDIO

DECODER

VIDEO

DECODER