Circuit Descriptions, Abbreviation List, and IC Data Sheets

EN 126

LC4.9E AA

9.

•

For the case of AP, the standard consists of BG/DK/I/M for

a Multi-System set. The diversity here will then depend on

the region. AP China can have a Multi-System and I/DK

version. For India, it might only be BG standard.

9.8.2

Functionality

The features available in the Hercules are as follows:

•

Treble and Bass Control.

•

Surround Sound Effect that includes:

–

Incredible Stereo.

–

Incredible Mono.

–

3D Sound (not for AV Stereo).

–

TruSurround (not for AV Stereo).

–

Virtual Dolby Surround, VDS422 (not for AV Stereo).

–

Virtual Dolby Surround, VDS423 (not for AV Stereo).

–

Dolby Pro-Logic (not for AV Stereo).

•

Bass Feature that includes:

–

Dynamic Ultra-Bass.

–

Dynamic Bass Enhancement.

–

BBE (not for AV Stereo).

•

Auto-Volume Leveler.

•

5 Band Equalizer.

•

Loudness Control.

All the features stated are available for the Full Stereo versions

and limited features for the AV Stereo

9.8.3

Audio Amplifier

The audio amplifier part is very straightforward. It uses two

integrated TDA8931T power amplifiers for the L and R

channels; each amplifier IC is able to deliver a maximum output

of 20 W

RMS

continuously in a 4-6 ohm speaker without needing

a heatsink.

The operating supply for the amplifier may range from 12 V to

32 V; in the LC04x TV set, depending on the model, supply

voltages of 18 V (for the 5 W / 8 ohm version) or 24 V (for the

15 W / 4 ohm version) are used.

Muting is done via the SOUND_ENABLE line connected to pins

7 of both amplifier-ICs, which comes from the Hercules.

9.8.4

Audio: Lip Sync

No Lip Sync adjustments are neccessary in this model.

9.9

Control

9.9.1

Hercules

The System Board has two main micro-controllers on board.

These are:

•

On-chip x86 micro-controller (OCM) from Genesis LCD or

plasma TV/Monitor Controller.

•

On-chip 80C51 micro-controller from Philips

Semiconductor UOCIII (Hercules) series.

Each micro-controller has it own I

2

C bus which hosts its own

internal devices.

The Hercules is integrated with the Video and Audio Processor.

For dynamic data storage, such as SMART PICTURE and

SMART SOUND settings, an external NVM IC is being used.

Another feature includes an optional Teletext/Closed Caption

decoder with the possibility of different page storage depending

on the Hercules type number.

9.9.2

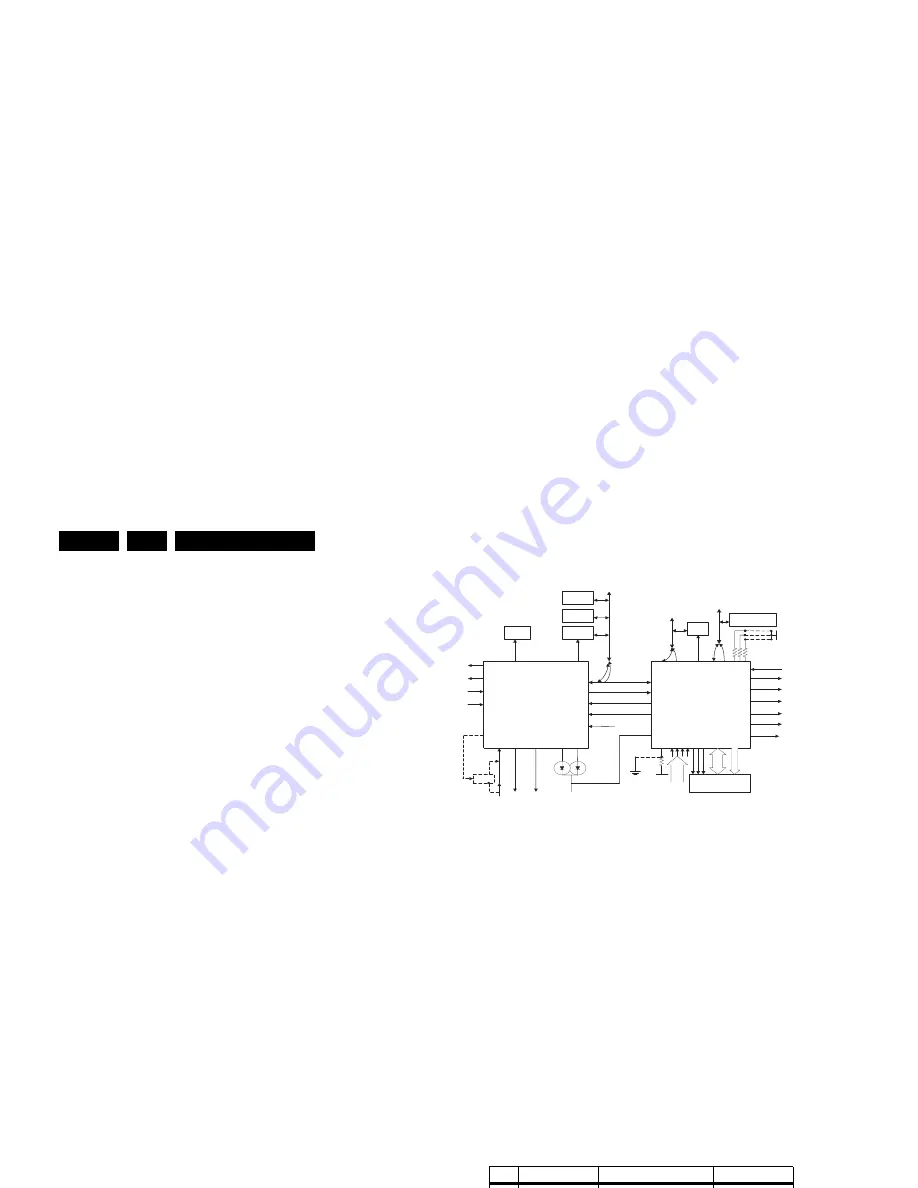

Block Diagram

The block diagram of the Micro Controller application is shown

below.

Figure 9-7 Micro Controller block diagram

9.9.3

Basic Specification

The Micro Controller operates at the following supply voltages:

•

+3.3 V

DC

at pins 4, 88, 94, and 109.

•

+1.8 V

DC

at pins 93, 96, and 117.

•

I

2

C pull up supply: +3.3V

DC

.

9.9.4

Pin Configuration and Functionality

The ports of the Micro Controller can be configured as follows:

•

A normal input port.

•

An input ADC port.

•

An output Open Drain port.

•

An output Push-Pull port.

•

An output PWM port.

•

Input/Output Port

The following table shows the ports used for the LC04 control:

Table 9-2 Micro Controller ports overview

The description of each functional pin is explained below:

Pin

Name

Description

Configuration

97

INT0/ P0.5

IR

INT0

98

P1.0/ INT1

TV_IRQ

INT2

99

P1.1/ T0

TV_SC_COM

P1.1

102

P0.4/ I2SWS

EXT_MUTE

P0.4

103

P0.3/ I2SCLK

Lip Sync

I2SCLK

104

P0.2/ I2SDO2

NVM_WP

P0.2

105

P0.1/ I2SDO1

Lip Sync

I2SDO1

106

P0.0/ I2SDI/O Lip Sync

I2SDI/O

107

P1.3/ T1

PC-TV_LED

P1.3

108

P1.6/ SCL

SCL

SCL

109

P1.7/ SDA

SDA

SDA

111

P2.0/ TPWM

SOUND_ENABLE

P2.0

112

P2.1/ PWM0

(for future use)

-

113

P2.2/ PWM1

(for future use)

-

114

P2.3/ PWM2

SEL_IF

P2.3

115

P3.0/ ADC0

Light Sensor - SDM

ADC0

116

P3.1/ ADC1

STATUS_1

ADC1

119

P3.2/ ADC2

STATUS_2

ADC2

120

P3.3/ ADC3

KEYBOARD

ADC3

122

P2.4/ PWM3

STANDBY

P2.4

123

P2.5/ PWM4

(for future use)

-

126

P1.2/ INT2

(for future use)

-

127

P1.4/ RX

HERC_RESET

-

128

P1.5/ TX

POWER_DOWN

P1.5

HERCULES

SCALER

T

u

ner

ComPair

N

V

M

So

u

nd

Amp

MUX

N

V

M

GPROBE for De

bu

g

or ComPair(Scaler)

SDA

SCL

T

V

_IRQ

T

V

_SC_COM

+3

V

3STBY

1407

1406

1405

PC_DET

SD_PCHD_SEL

PC_HD_SEL

POWER_DOWN

LAMP_ON_OFF

PANEL_PWR_CTL

HD_FILTER

BACK_LIGHT_ADJ1

Flash ROM

83

GPIO2

N

V

M_WP

IIC BUS 2

93

N

V

RAM

_SDA

92

N

V

RAM

_SCL

72

71

187

193

194

85

(GPIO4)

88

(GPIO5)

89

(GPIO6)

68

(PBIAS)

67

(PPWR)

99

(PWM1)

98

(GPIO11/

PWM0)

78 DDC_SDA_

V

GA

77 DDC_SCL_

V

GA

82 GPIO1

81 GPIO0

+3

V

3STBY

111

GPIO23

90 GPIO7

ROM_ADD0-17

ROM_DATA0-7

5 6 7

103 106 107 108

HIGH or

LOW

level inp

u

t

IIC BUS1

N

V

M_WP

So

u

nd_Ena

b

le

HREC

RST

Sel IF/

SDM

Stat

u

s1

Light

Sense

T

V

_IR

RC

P50_LINE_IT

V

_IR_SW

EXT_MUTE

Stand

b

y

POWER

DOWN

127

P1.4

114

P2.3

116

ADC1

115

ADC0

123

P2.5

97

INT0

102

P0.4

122

P2.4

126

INT2

128

P1.5

SDA 109

SCL 108

INT1 98

P1.1 99

Key

b

oard

ADC3 120

111

P2.0

104

P0.2

E_14490_062.eps

160904