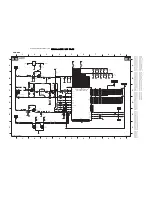

Circuit Diagrams and PWB Layouts

79

LC4.9E AA

7.

SSB: Audio Delay Line (Lipsync)

EN

C1

1D

EN

C1

1D

2C1

14

1

3

11

10

9

8

7

6

5

4

3

2

1

0

2EN

3

2k-1

0

A

A,1D

12

A

G2

C2

G1

1+

CT=0

CTR

8

(CT=255)Z4

2D

3

4

EN

3

C2

G1

1+

CT=0

CTR

8

(CT=255)Z4

2D

3

4

EN

3

AUDIO DELAY LINE (LIP

S

YNC)

COUNTER

COUNTER

LATCH

LATCH

2V

3

2V

3

5V

3

5V

3

2V6

2V6

2V6

2V6

2V6

2V6

2V6

5V

3

2V5

2V5

2V5

2V5

2V5

2V5

2V5

2V5

2V

3

5V

3

2V

3

5V

3

5V

3

2V6

2V6

2V6

2V6

2V6

2V6

2V6

2V

3

0V2

5V

3

2V

3

2V6

2V

3

5V

3

2V6

RE

S

*

RE

S

RE

S

RE

S

RE

S

RE

S

RE

S

RE

S

RE

S

450

3

4504

LCD PDP

N

Y

Y

N

*

*

4510 C9

4511 C9

4512 C9

451

3

C9

4514 C9

5501 A1

7501 A1

7502 B

3

750

3

F1

7504 F6

7505 C7

7506 C

8

F501 A2

F502 B2

F50

3

C10

F504 D10

F505 F10

I501 F5

I502 F6

I50

3

E2

I504 F2

I505 F2

A

B

C

D

E

F

A

B

C

D

E

F

2501 A1

2502 B2

250

3

D1

2504 B7

2505 B9

2506 D10

2507 D10

250

8

F6

2509 F7

3

501 F6

3

502 F6

4501 E2

4502 F2

450

3

F2

4504 F2

4505 F

3

4506 F

3

4507 C9

450

8

C9

4509 C9

1

2

3

4

5

6

7

8

9

10

1

2

3

4

5

6

7

8

9

10

I504

I505

I50

3

22

2

8

27

F502

20

11

12

1

3

15

16

17

1

8

19

14

9

10

24

25

26

1

2

3

4

5

21

2

3

6

7

8

CY62256LL-70ZC

7502

3

2kx

8

RAM

8

2p

250

8

470p

2507

20

33

0p

2506

11

1

19

1

8

17

16

15

14

1

3

12

2

3

4

5

6

7

8

9

10

12

20

74HC57

3

PW

7505

10

11

1

19

1

8

17

16

15

14

1

3

2

3

4

5

6

7

8

9

74HC57

3

PW

7506

F505

4504

4506

I502

I501

F504

4514

F50

3

451

3

4512

4511

4509

4510

450

8

4507

+5VD

4505

4502

4501

450

3

7504

BC

8

47BW

3

502

47K

3

501

470R

2509

8

2p

+5VD

2505

100n

+5VD

+5VD

2504

100n

2502

100n

+5VD

+5VD

250

3

100n

100n

2501

+5VD

+5VD

+5VD

F501

5501 1

u

0

6

7

1

3

9

VCC

16

+5V

S

WI

GND

8

14

15

1

2

3

4

5

11

12

10

5

6

7

1

3

9

16

VCC

750

3

M74HC590T

GND

8

14

15

1

2

3

4

7501

M74HC590T

11

12

10

I2

S

DI1

I2

S

CLK

I2

S

DO1

B4

B4

3

1

3

9 12

3

6141.1

G_15

3

51_004.ep

s

0

8

0906