IC Data Sheets

8.

8.3

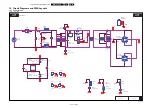

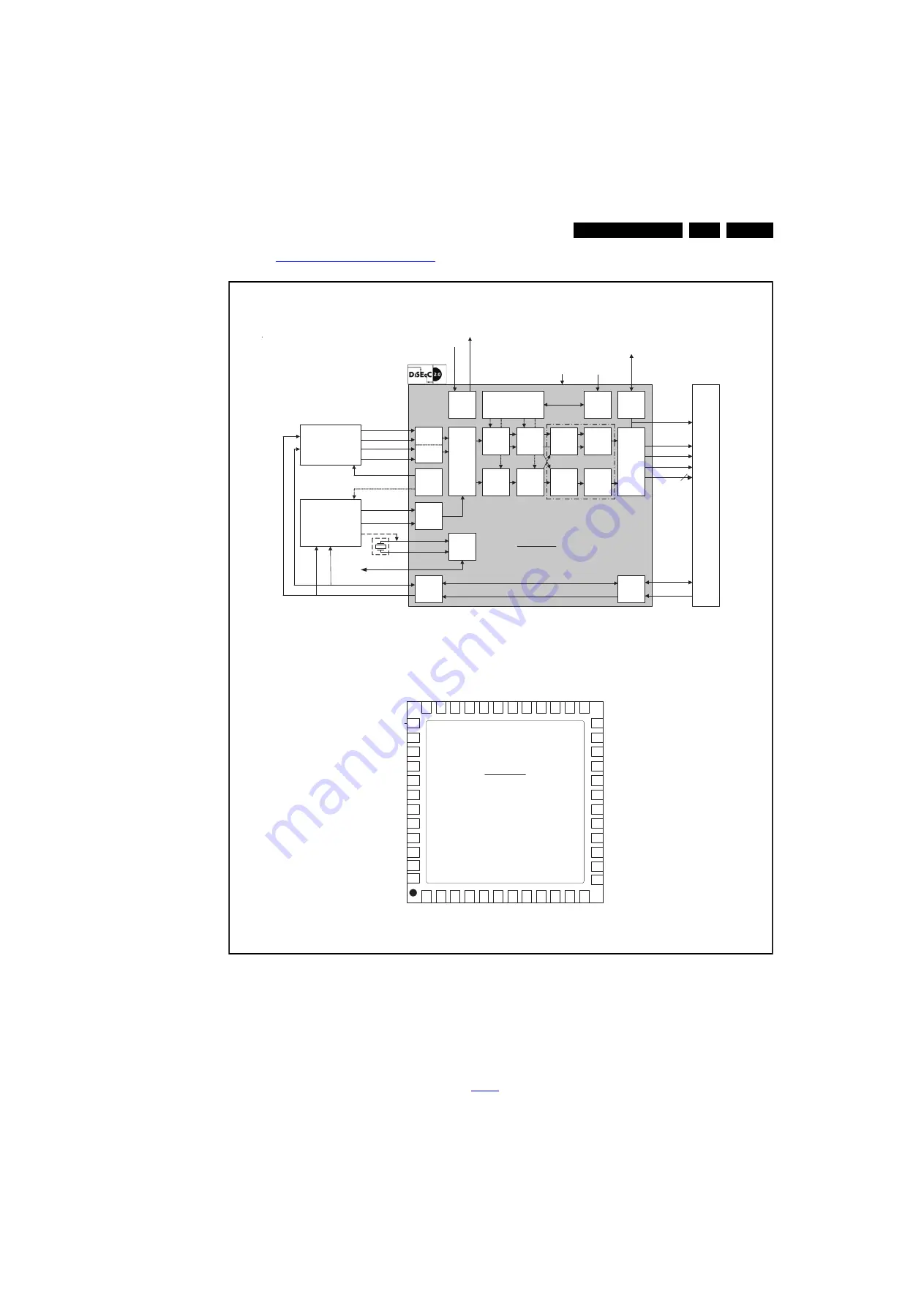

Diagram

, B05, SI2169-C50 (IC U201)

Figure 8-4 Internal block diagram and pin configuration

20030_302.eps

Block diagram

Pinning information

Si2169C

(GND_PAD)

QFN-48

7x7mm

34

35

36

21

22

23

24

3

4

5

33

20

6

32

7

28

29

30

31

27

8

9

10 11 12

15

16

17

18

19

40

39

38

37

41

46

45

44

43

42

MP

_A

S_ADC_IP

S_ADC_IN

S_ADC_QP

S_ADC_QN

SDA_MAST

SCL_MAST

NC

TC_ADC_P

TC_ADC_N

DI

S

E

QC_

OUT

MP

_B

S

CL

_

H

O

S

T

DI

S

EQC_

CMD

GND

S

DA_

H

O

S

T

T

S

_V

AL

DI

S

EQC_

IN

TS_DATA[1]

TS_DATA[5]

TS_DATA[4]

TS_DATA[3]

GND

VDD_VIO

TS_DATA[2]

TS_DATA[0]/TS_S

TS_CLK

TS_SYNC

47

14

T

S

_

DAT

A[7

]

RE

S

ET

B

XT

AL_

I/C

LK_

I

XT

AL_

O

GND

VDD

_

VCO

R

E

VDD_

VA

N

A

ADDR

GND

GPI

O_

0

48

13

2

1

26 25

TS_DATA[6]

T

S

_

E

RR/GP

IO

CLK_IN_OUT

GND

VDD_VCORE

V

DD_

VCORE

VD

D_V

IO

VDD_VCORE

MP

_D

MP

_

C

SI2169-C50

HDTV MPEG

S

.o.C.

Si2169C

HOST_SCL

HOST_SDA

FRONT

END

OSC

& PLL

x(A)PSK

QAM

DEMOD

S_ADC_IN

S_ADC_IP

S_ADC_QN

S_ADC_QP

ADC (I)

ADC (Q)

EQUAL-

IZER

I

2

C

SWITCH

TUN_SDA

TUN_SCL

GPIO

CTRL

MP

EG T

S

IN

TE

R

F

A

C

E

I

2

C

I/F

MP_C/_D (Sat.)

GP

IO_0

RESETB

1.2, 3.3V

DSP &

SYNCHRO

DVB-T2/T/C/S/S2

FEC MODULE

OFDM

DEMOD

EQUAL-

IZER

DiSEqC

TM

2.0

DI

S

EQC

_

IN

DI

S

EQC

_

O

U

T

TC_ADC_P

TC_ADC_N

AGCs

ADC

MP_A/_B (T & C)

Ext. Clk or Xtal

QPSK/8PSK/xAPSK

Satellite

ZIF Tuner

Silicon Labs

(Si217x/5x/4x)

TV Tuner

CLK_IN_OUT

LDPC

BCH

VITERBI

RS

TS_ERR/

GPIO_1

TS_SYNC

TS_VAL

8

TS_CLK

TS_DATA