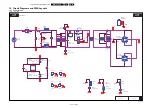

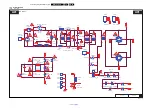

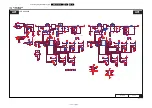

9.

Block Diagrams

9.2

Block diagram 6801 series

20151_400.eps

G P A 2 2

O P W M 1

2 X ( D D R 2 5 1 2 M b i t s )

1333 MHz

e M M C

8 GB

1 X D D R 3

1833

4G bit

2 X D D R 3

1833

4G bit

2 X D D R 3

1833

4G bit

E t h e r n e t

U S B 3 . 0

U S B 2 . 0

U S B 2 . 0

P a r a l l e l T S [ D 0 : D 7 ]

U S B 3 . 0

U S B 2 . 0

U S B 2 . 0

U S B 2 . 0

A n a l o g

I/O

H D M I

Rx

I F i n p u t

L V D S / V x 1

Transmitter

M T 5 5 9 3 U +

Dual CA17 + 2xCA7

1MB L2 CAche

Mali T624 MP3

ME/MC

HEVC UHD50/60

D V B -

T/T2/S/S2

DEMOD

sI216X

R G B / C V B S

H D M I p o r t 3

H D M I p o r t 2

H D M I p o r t 1

H D M I p o r t 0 + M H L

Y P b P r

A u d i o L / R

8-Lane V X 1

Audio AMP

TAS5760

NT72333

UHD50 FRC

MEMC

UHD50

Tcon

Audio AMP

APA2010

PWM

I2S

Digital

ADAC

ADAC

SPI Flash

16Mb

Wi-Fi 11AC

BT

Disp Control (X4)

IF

PWM

Bluetooth

Wi-Fi

RJ45

Speaker

Headphone

Bathroom SPK

(Mono)

8-Lane V X 1

DVB-C/T/T2

DVB S/S2

Hybrid

Tuner

Satelite

Tuner

SPI-select

SPI

switch

AMBI-SPI-OUT

Dp/Dn

Video

Audio

S C A R T

BACKLIGHT

BL-DIMMING

AMBI-LIGHT

A M B I - S P I - M T K ( S t a t i c )

AMBI-SPI-NVT

(Dynamic)

H D M I

TS input

T x R x - p / n

D p / D n + D p / D n _ T x R x

Dp/Dn

D p / D n

FHD 50 Hz

F o r H T V o n l y

Uart/RS232

R J 4 8 S X P

Uart & RS232

U0TxRx

U H D 5 0 H z