4-3

4-3

PCS 99 458

Abbreviations and Pin-description of CD Ics

SERVO PROCESSOR SAA7325H

SYMBOL

PIN

DESCRIPTION

HFREF

1

comparator common mode input

HFIN

2

comparator signal input

ISLICE

3

current feedback output from data slicer

V

SSA1

4

(1)

analog ground 1

V

DDA1

5

(1)

analog supply voltage 1

I

ref

6

reference current output pin

V

RIN

7

reference voltage for servo ADC's

D1

8

unipolar current input (central diode signal input)

D2

9

unipolar current input (central diode signal input)

D3

10

unipolar current input (central diode signal input)

D4

11

unipolar current input (central diode signal input)

R1

12

unipolar current input (satellite diode signal input)

R2

13

unipolar current input (satellite diode signal input)

V

SSA2

14

(1)

analog ground 2

CROUT

15

crystal/resonator output

CRIN

16

crystal/resonator input

V

DDA2

17

(1)

analog supply voltage 2

LN

18

DAC left channel differential output - negative

LP

19

DAC left channel differential output - positive

V

neg

20

DAC negative reference input

V

pos

21

DAC positive reference input

RN

22

DAC right channel differential output - negative

RP

23

DAC right channel differential output - positive

SELPLL

24

selects whether internal clock multiplier PLL is used

TEST1

25

test control input 1; this pin should be tied LOW

CL16

26

16.9344 MHz system clock output

DATA

27

serial d4(1)ata output (3-state)

WCLK

28

word clock output (3-state)

SCLK

29

serial bit clock output (3-state)

EF

30

C2 error flag output (3-state)

TEST2

31

test control input 2; this pin should be tied LOW

KILL

32

kill output (programmable; open-drain)

V

SSD1

33

(1)

digital ground 2

V2/V3

34

versatile I/O: input versatile pin 2 or output versatile pin 3 (open-drain)

WCLI

35

word clock iutput (for data loopback to DAC)

SDI

36

serial data input (for data loopback to DAC)

SCLI

37

serial bit clock input (for data loopback to DAC)

RESET

38

power-on reset input (active LOW)

SDA

39

microcontroller interface data I/O line (open-drain output)

SCL

40

microcontroller interface clock line input

Abbreviations and Pin-description of CD Ics

SERVO PROCESSOR SAA7325H

SYMBOL

PIN

DESCRIPTION

RAB

41

microcontroller interface R/W and load control line input (4-wire bus mode)

SILD

42

microcontroller interface R/W and load control line input (4-wire bus mode)

STATUS

43

servo interrupt request line/decoder status register output (open-drain)

TEST3

44

test control input 3; this pin should be tied LOW

RCK

45

subcode clock input

SUB

46

P-to-W subcode bits output (3-state)

SFSY

47

subcode frame sync output (3-state)

SBSY

48

subcode block sync output (3-state)

CL11/4

49

11.2896 MHz or 4.2336 MHz (for microcontroller) clock output

V

SSD2

50

(1)

digital ground 3

DOBM

51

bi-phase mark output (externally buffered; 3-state)

V

DDD1(P)

52

(1)

digital supply voltage 2 for periphery

CFLG

53

correction flag output (open-drain)

RA

54

radial actuator output

FO

55

focus actuator output

SL

56

sledge control output

V

DDD2(C)

57

(1)

digital supply voltage 3 for core

V

SSD3

58

(1)

digital ground 4

MOTO1

59

motor output 1; versatile (3-state)

MOTO2

60

motor output 2; versatile (3-state)

V4

61

versatile output pin 4

V5

62

versatile output pin 5

V1

63

versatile intput pin 1

LDON

64

laser drive on output (open-drain)

Note : All supply pins must be connected to the same external power supply voltage.

Summary of Contents for AZ-2030

Page 4: ......

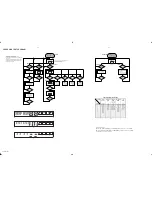

Page 14: ...BLOCK DIAGRAM 5 1 5 1 PCS 107 281 For AZ2035 only For AZ2030 only ...

Page 15: ...WIRING DIAGRAM 5 2 5 2 PCS 107 282 ...

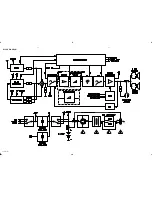

Page 16: ...FRONT BOARD CIRCUIT DIAGRAM 6 1 6 1 PCS 107 283 ...

Page 17: ...FRONT BOARD LAYOUT DIAGRAM 6 2 6 2 PCS 107 284 ...

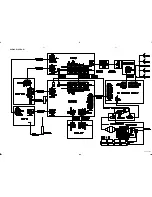

Page 18: ...AF POWER BOARD CIRCUIT DIAGRAM 7 1 7 1 PCS 107 285 ...

Page 20: ...FEATURE BOARD CIRCUIT DIAGRAM 8 1 8 1 PCS 107 287 ...

Page 21: ...FEATURE BOARD LAYOUT DIAGRAM 8 2 8 2 PCS 107 288 ...