Circuit Descriptions, List of Abbreviations, and IC Data Sheets

EN 108

DPTV565 AA

9.

9.7.9

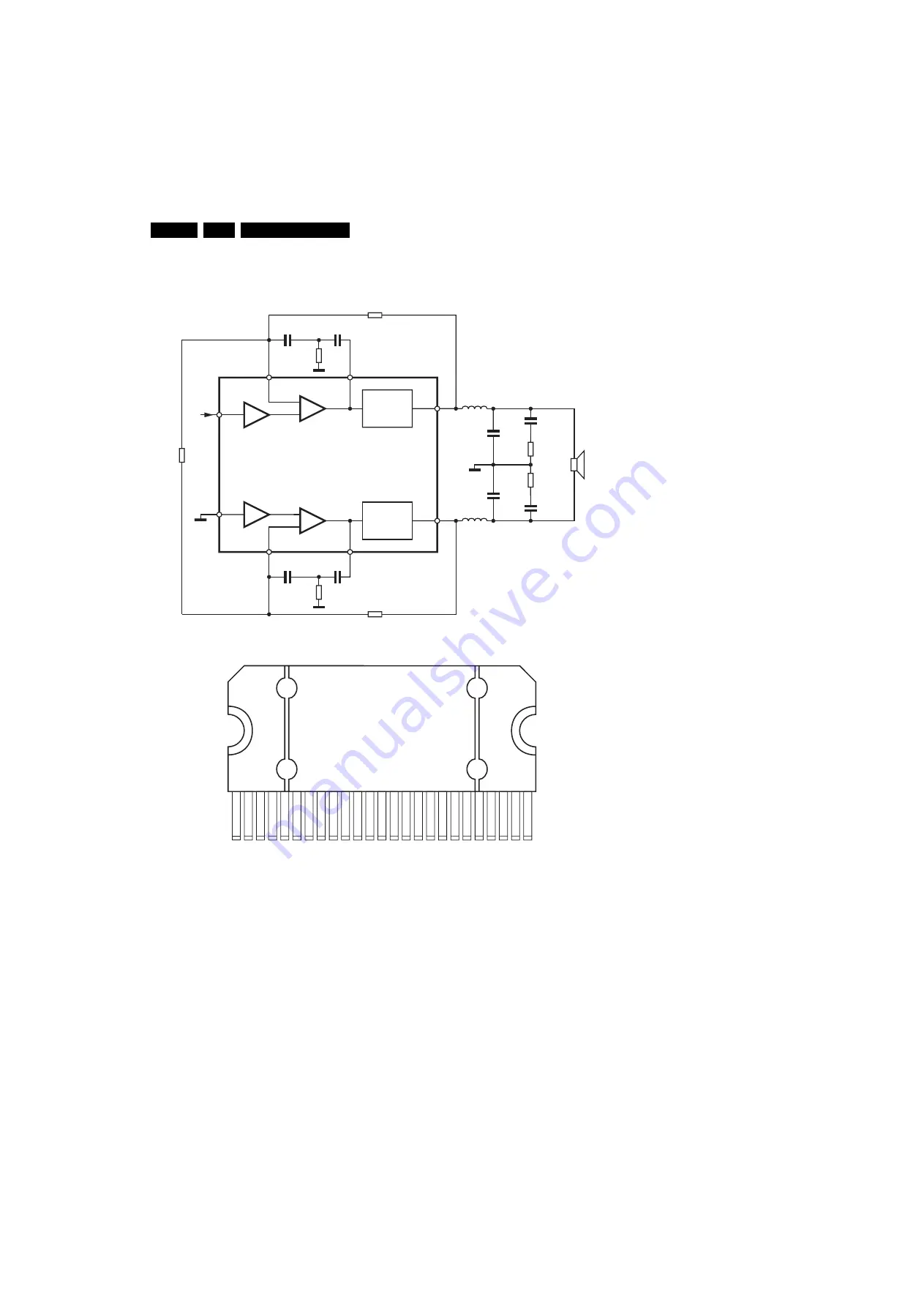

Diagram S7, TDA7490 (IC7700)

Figure 9-53 Internal block diagram and pin configuration

PWM-stage

PRE

+

-

-

+

470pF

470pF

R4

68K

R5 52.3K

L9 30

µ

INPUT

C23

235nF

PWM-stage

L10 30

µ

C26

470nF

dumping

(common

mode)

The LC filter is optimized for 8

Ω

(<->LC filter for 4

Ω

in single-ended)

It hos to be changed for other loads

C24

235nF

C29

470nF

R28

10

R27

10

R25

Rload

PRE

470pF

470pF

R61

68K

R62 52.3K

7

9

10

18

19

17

23

3

R63

4.7K

Int.

Int.

C40

C60

C59

C41

V-

C

C

V-

C

C

1

T

U

O

V

+

C

C

1

T

O

O

B

E

T

U

M-

Y

B

T

S

1

D

E

E

F

C

S

O

2

D

E

E

F

1

NI

1

T

V

5

+

D

N

G

F

E

R

R

U

C

2

T

V

5-

3

D

E

E

F

2

NI

4

D

E

E

F

.

C.

N

2

T

O

O

B

V

+

C

C

2

T

U

O

V-

C

C

g

er

V

1

25

Internal Block Diagram

Pin Configuration

E_15000_124.eps

170305