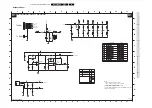

60

DPTV565 AA

7.

Circuit Diagrams and PWB Layouts

ACS Module

14K

OF 1.25V

REF VOLT

TIMER

LOGIC&

RESET

NO

T USED

NO

T USED

18

17

L

G

AUTO CONVERGENCE

8

12

11

10

16

17

E

D

3

1

B

C

D

18

A

2

F

G

20

19

4

RESET TESTPOINT

COMPUTER

15

NO

T USED

NO

T USED

E

16

15

9

9

TEST CONNECT

CONNECTOR

DEVELOPMENT

N

J

L

M

N

O

SCL_B

RESET

RESET

I2C BUS B

K

3

4

5

6

IIC BUS

5

O

H

I

7

14

20

K

F

NO

T USED

NOT USED

NOT USED

NO

T USED

8

B

10

11

12

13

14

P

19

P

C

H

I

J

OSD "OR" CIRCUIT

M

7

GND

6

A

1

2

SDA_B

BAS216

6312

3331

100R

2-M15

1K0

3328

100R

3323

100R

3351

2

3

4300

10p

2320

1300

JQ-S

1

+3.3V

BAS216

6310

BAS216

6315

BAS216

6313

BAS216

6311

+5V

+5V

3322

100R

1-N14

2310

10n

100R

3308

1K0

3329

F023

7017

BC847B

47R

3315

100n

2314

3348

100R

1-E2

BAS216

6308

3201

100R

100R

3325

4302

2-L15

F301

+9V

F024

100R

3350

1-N8

100R

3200

2312

100n

10p

2319

100R

3309

4303

10p

2317

2-I15

BAS216

6309

+5V

2-K3,1-N8

2-M3,1-G2

+5V

2-D18

7015

BC847B

1K0

3326

1-N15

10K

3332

1-N14

1-I2

47R

3317

4305

2-M15

2-M15

F028

3314

47R

4301

+5V

2-H15

4304

1-E2

1-F2

NC

6

PFI

4

PFO_

5

RESET

8

RESET_

7

VDD

2

2-H15,1-D2

2-K3

7301

TPS3707-33D

GND

3

MR_

1

100R

3307

1301

B6B-EH-A

1

2

3

4

5

6

+5V

F025

3324

100R

1302

RT-01T-1.0B

1

1-C2

2-E18

2-H15,1-D2

BC847B

7014

2-K15,1-I2

2313

100n

2-J3

2315

100n

100R

3349

10p

2318

100R

3306

BAS216

6314

1K0

3327

2-J3,1-G2

F026

1-C2

3316

47R

ADC_GND

2-I15

1-E2

BC847B

7016

F027

2K2

3333

BLANK_uP

BLUE_ST

BLUE_uP

GRN_ST

GRN_uP

RED_ST

RED_uP

SH_CLEAR

OPTT

SYNC_V

SCL_B

SDA_B

SDA_A_Rxd

Rxd

SDA_A

SCL_A

SCL_A_Txd

BLANK_ST

Txd

Reset_ST

R

G

B

BLANK

Reset_N

SCL_C

SDA_C

ADC_IN

ACS Module

13

H3

H3

E_15000_038.eps

191004

3135 013 3233.3