Circuit Descriptions, List of Abbreviations, and IC Data Sheets

EN 100

DPTV565 AA

9.

9.7

IC Data Sheets

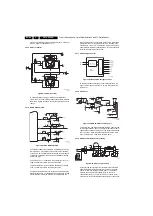

This section shows the internal block diagrams and pin layouts

of ICs that are drawn as "black boxes" in the electrical diagrams

(with the exception of "memory" and "logic" ICs).

9.7.1

Diagram ACS2, SAA5667HL (IC7100)

Figure 9-45 Internal block diagram and pin configuration

MICROPROCESSOR

(80C51)

SRAM

256 BYTES

ROM

(128 K or 192 KBYTES)

MEMORY

INTERFACE

DISPLAY

R

G

B

VDS

HSYNC

VSYNC

CVBS

DATA

CAPTURE

DRAM

(14 KBYTES)

TV CONTROL

AND

INTERFACE

I

2

C-bus, general I/O

DISPLAY

TIMING

CVBS

DATA

CAPTURE

TIMING

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

P3.7

P0.4/INT4

A6

P0.3/INT3

VPE

ALE

PSEN

P0.2/INT2

P0.1/TX

P0.0/RX

A7

EA

P0.5

VSSP

VSSC

WR

RD

A14

A15_LN

P3.3/ADC3

P3.2/ADC2

P3.1/ADC1

A17_LN

P3.0/ADC0

P2.7/PWM6

RAMBK.0

VDS

HSYNC

P3.5/INT5

VSYNC

ROMBK.2

ROMBK.1

ROMBK.0

P3.6

VSSP

INTD

VSSC

VDDC

A11

A10

A9

A8

MOVX_WR

OSCGND

XTALIN

XTALOUT

RESET

RESET

MOVX_RD

VDDP

0

0

1

9

9

8

9

7

9

6

9

5

9

4

9

3

9

2

9

1

9

0

9

9

8

8

8

7

8

6

8

5

8

4

8

3

8

2

8

1

8

0

8

9

7

8

7

7

7

6

7

M

W

P

T/

0.

2

P

V

C

S

S

5

M

W

P/

6.

2

P

4

M

W

P/

5.

2

P

3

M

W

P/

4.

2

P

2

M

W

P/

3.

2

P

1

M

W

P/

2.

2

P

0

M

W

P/

1.

2

P

7

D

A

6

D

A

5

D

A

4

D

A

3

D

A

2

D

A

1

D

A

0

D

A

1

A

D

S/

5.

1

P

1

L

C

S/

4.

1

P

0

A

D

S/

7.

1

P

0

L

C

S/

6.

1

P

I

T/

3.

1

P

0

T

NI/

2.

1

P

0

T/

1.

1

P

N

L

_

6

1

A

1

T

NI/

0.

1

P

5

A

4

A

6.

0

P

2

T/

7.

0

P

V

A

S

S

0

S

B

V

C

1

S

B

V

C

K

B

_

5

1

A

R

E

T

LI

F

_

C

N

Y

S

F

E

RI

3

1

A

2

1

A

3

A

2

A

1

A

E

M

A

R

F

E

P

V

R

O

C

X

E

2

T/

7

M

W

P/

4.

3

P

V

A

D

D

B

G

R

0

A

1.

K

B

M

A

R

6

2

7

2

8

2

9

2

0

3

1

3

2

3

3

3

4

3

5

3

6

3

7

3

8

3

9

3

0

4

1

4

2

4

3

4

4

4

5

4

6

4

7

4

8

4

9

4

0

5

GSA020

SAA56xx

Internal Block Diagram

Pin Configuraton

E_15000_115.eps

170305