EN 36

3139 785 33120

7.

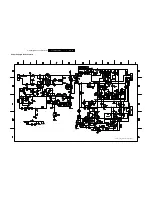

Circuit Diagrams and PWB Layouts

Digital: IEEE 1394 Physical Layer

0

1

R

0

1

FILTER

DGND

LKON

D

PC

CTL

D

D

VL

L

P

S

H_

D

N

G

AGND

DVDD

D

N

GL

L

P

AVDD

TPA+

TPA-

TPB+

TPB-

7

6

5

4

3

2

1

0

1

0

LREQ

SYSCLK

RESET

PD

TPBIAS

0

1

C

2

XO

ISO

LPS

TESTM

SE

SM

CPS

XI

G

H

I

A

B

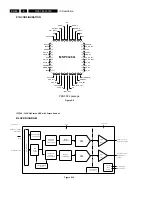

IEEE1394 Physical Layer

)

Y

H

P(

tr

o

ps

na

r

T -

la

ci

sy

h

P

49

31

E

E

EI

14

A

B

C

D

E

F

11

12

13

14

1

C

D

E

F

G

H

I

1351 D5

2301 D6

1

2

3

4

5

6

7

8

9

10

2321 G5

2341 G9

2343 G9

2351 D5

2352 E5

2

3

4

5

6

7

3332 F5

3341 F9

3342 F9

3343 F9

3344 F9

8

9

10

11

12

13

2302 D6

2303 D6

2304 D6

2305 D7

2306 D7

2307 D7

2361 E5

3301 E5

3302 F5

3303 G8

3304 G8

3305 E8

3306 F7

3307 F7

3308 F7

3321 F5

3322 G5

3331 F5

T308 F7

T309 E7

T310 F6

T311 F7

T312 E7

3345 G9

3351 E5

3360 E5

3361 E5

3362 E5

4361 E5

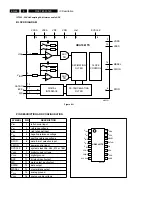

IEEE1394 Link - Physical (LNK)

T313 E7

T314 E7

T315 F6

T316 F6

T317 C6

T321 F6

T351 E6

T352 E6

5301 C6

7301 D6

T301 E7

T302 E7

T303 E7

T304 E7

T305 E7

T306 E7

T307 E7

3304

10K

5301

BLM18P

T311

24

33

n0

01

12

32

%1

R6

5

T307

T321

T312

T305

27

31

42

43

1K0

3301

33

34

37

23

24

1

22

30

29

28

94

19

13

48

16

17

18

12

14

04

10

11

41 64

74

12 44 54

38

39

53

20

2

3

15

4

5

6

7

8

9

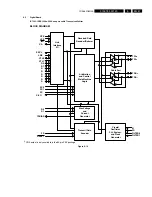

1-PORT CABLE

TSB41AB1PHP

7301

62 23 63

52

TRANCEIVER

ARBITER

Φ

p0

22

34

32

0

M1

15

33

T301

%1

34

33

24M576 AT-51CD2

1351

R6

5

7

K4

100n

2305

22

33

2302

T316

100n

T315

3306

680R

T314

680R

3307

4361

T304

T308

%1

1

K5

54

33

2303 100n

0u

1

T351

T352

14

32

3362

1K0

T303

10K

3303

1K0

3361

T310

2352 33p

25V

10u

2301

100n

2304

3302

10K

750R

3332

1%

1%

5K6

3331

R6

5

44

33

%1

1K0

3360

T317

T302

R6

5

14

33

%1

100n

2361

T309

3305

22R

100R

3321

2306 100n

T313

T306

2307 100n

3308

680R

33p

2351

3V3I

3V3I

3V3BE

3V3I

3V3I

3V3I

3V3I

3139_243_34464_130_03_a2.pdf 2006-03-20