EN 52

3139 785 33120

8.

IC Description

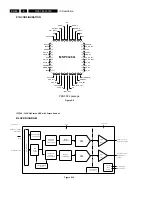

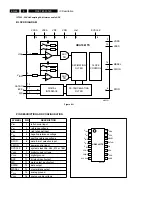

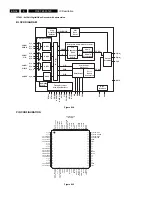

IC7401 - 4x10bit DigitalVideo Decoder with microvision

BLOCK DIAGRAM

Composite and S-Video Processor

Y/C

Separation

5-line

Adaptive

Comb

Luma

Processing

Chroma

Processing

ADC1

ADC2

ADC3

ADC4

M

U

X

Component

Processor

CVBS/Y

C

Y/G

Pb/B

Pr/R

Gain/Offset

Color

Space

Conversion

C

Y

Output

Formatter

Y[9:0]

YCbCr

VBI

Data

Slicer

Copy

Protection

Detector

C[9:0]

Host

Interface

Timing Processor

with Sync Detector

VI_1_A

VI_1_B

VI_1_C

VI_2_A

VI_2_B

VI_2_C

VI_3_A

VI_3_B

VI_3_C

VI_4_A

CVBS/

Y/G

CVBS/

Pb/B/C

CVBS/

Pr/R/C

CVBS/Y

CVBS/Y/G

Analog Front End

Sampling

Clock

GPIO

FSS

HS/CS

VS/VBLK

FID

A

VID

XT

AL1

XT

AL2

DA

TACLK

RESETB

GLCO

DR

DG

DB

FSO

PWDN

SCL

SDA

YCbCr

Figure 8-14

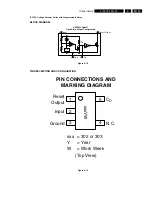

PIN CONFIGURATION

22 23

C_6/GPIO/RED

C_7/GPIO/GREEN

C_8/GPIO/BLUE

C_9/GPIO/FSO

DGND

DVDD

Y_0

Y_1

Y_2

Y_3

Y_4

IOGND

IOVDD

Y_5

Y_6

Y_7

Y_8

Y_9

DGND

DVDD

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

24

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

VI_1_B

VI_1_C

CH1_A33GND

CH1_A33VDD

CH2_A33VDD

CH2_A33GND

VI_2_A

VI_2_B

VI_2_C

CH2_A18GND

CH2_A18VDD

A18VDD_REF

A18GND_REF

CH3_A18VDD

CH3_A18GND

VI_3_A

VI_3_B

VI_3_C

CH3_A33GND

CH3_A33VDD

25 26 27 28

PFP PACKAGE

(TOP VIEW)

79 78 77 76 75

80

74

72 71 70

73

29 30 31 32 33

69 68

21

67 66 65 64

34 35 36 37 38 39 40

63 62 61

VI_1_A

CH1_A18GND

CH1_A18VDD

PLL_A18GND

PLL_A18VDD

XT

AL2

XT

AL1

VS/VBLK/GPIO

HS/CS/GPIO

FID/GPIO

C_0/GPIO

C_1/GPIO

DGND

DVDD

C_2/GPIO

C_3/GPIO

C_4/GPIO

C_5/GPIO

IOGND

IOVDD

CH4_A33VDD

CH4_A33GND

VI_4_A

CH4_A18GND

CH4_A18VDD

AGND

DGND

SCL

SDA

INTREQ

DVDD

DGND

PWDN

RESETB

FSS/GPIO

A

VID/GPIO

GLCO/I2CA

IOVDD

IOGND

DA

TACLK

Figure 8-15