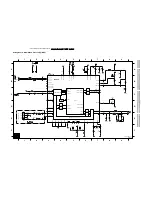

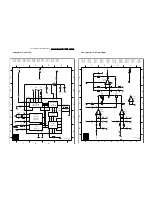

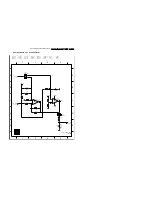

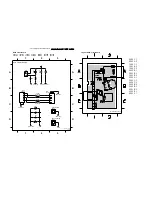

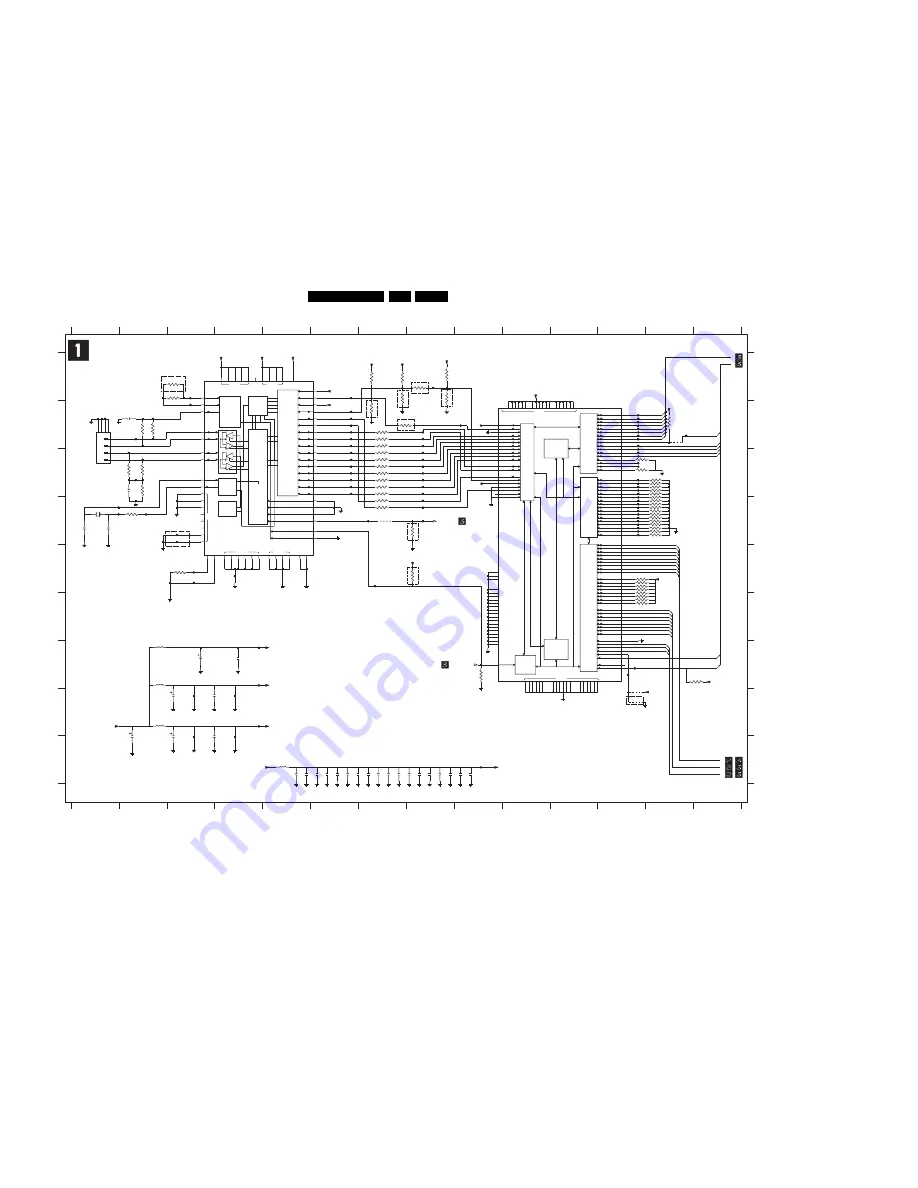

Circuit Diagrams and PWB Layouts

EN 119

DVDR880-890 /0X1

7.

DVIO Board: 1394 Interface

PLLGND

DVDD

AVDD

STATE

MACHINE

LOGIC

TRANSMIT

CLOCK

PLL

XTAL OSC

AGND

ENCODER

DATA

GENERATOR

CURRENT

AND

VOLTAGE

BIAS

LINK

INTERFACE

RECEIVED

DATA

DECODER/

TIMER

ARBITR’N

AND

CONTROL

NC

DGND

AV1 LAYER

ISOCHRONOUS

TRANSMITTER/RECEIVER

ASYNC

TRANSMITTER

AND

RECEIVER

CONTROL

AV1 LAYER

INTERFACE

8-BIT

REGISTERS

STATUS

AND

TRANSMITTER/RECEIVER

ISOCHRONOUS

LINK

CORE

12KB BUFFER

MEMORY

VDD

GND

A

B

C

D

1

2

3

4

5

6

7

8

9

10

11

12

13

14

E

F

G

H

I

A

B

C

D

E

F

G

H

I

1

2

3

4

5

6

7

8

9

10

11

12

13

14

FROM FRONT

DV INPUT PCB

LINK

PHY

1394 INTERFACE

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

OPTION

3124

47K

47K

3125

F189

F166

F167

5110

100MHZ

22K

3134

100MHZ

5109

56R

3178

F175

F198

F146

R0

41 R1

53

RESET_

2

SYSCLK

TEST0

29

TEST1

28

TESTM

27

37 TPA0+

36 TPA0-

35 TPB0+

34 TPB0-

38 TPBIAS0

59 XI

60 XO

LREQ

54

55

16

43

44

45

46

47

20

PC0

21

PC1

22

PC2

14

PD

57

58

56

PLLVDD

40

D2

9

D3

D4

10

D5

11

D6

12

D7

13

17

18

63

64

25

26

61

62

23

ISO_

15

LPS

1

48

49

50

30

31

42

51

52

CNA

3

24

CPS

4

CTL0

5

CTL1

19

C|LKON

6

D0

7

D1

8

3193

1R

7101

PDI1394

32

33

39

F601

F186

3133

22K

F134

3166

2163

270p

3165

56R

2K2

100n

2176

F131

100n

2152

F135

F157

F150

3139

10K

10K

3138

F108

F132

3119

47K

10K

3147

F126

100n

2197

2173

10u

24M576

1102

CX-11F

3197

47K

2196

100n

F191

3115

1K

F128

F602

2153

100n

2K2

3111

100n

2154

2182

10u

47R

3190

5

6

7

8

1

2

3

4

F153

1101

F116

3131

47K

F137

100n

47K

3120

F149

2194

3107

F130

3105

10R

10R

100n

2151

2170

12p

100n

2147

2181

100u

F174

3176

10R

F171

3172

10R

2146

100n

56R

3164

2171

12p

F127

F154

F136

3126

47K

100n

2184

47K

3100

100MHZ

5103

F118

3116

1R

F172

2174

100n

F117

9K1

3141

3140

10K

4103

F190

4100

F115

4102

10R

3174

47R

3188

10u

2175

F188

47K

3110

47K

3122

4101

47K

3130

5K1

3177

F101

F185

100n

2104

100n

2105

3173

56R

F107

3128

47K

F106

F113

3191

10R

100n

2156

3137

1R

2157

100n

F193

2150

100n

3121

47K

F165

100n

2149

10R

3171

F184

F102

F168

F161

47K

3132

F163

F197

35

24

18

12

6

70

F100

RESET

88

SCLK

TESTPIN1

62

TESTPIN2

63

TESTPIN3

64

61

78

84

90

95

107

113

120

132

138

54

44

RESERVED11

RESERVED12

72

104

RESERVED13

RESERVED14

105

129

RESERVED15

RESERVED16

130

144

RESERVED17

50

RESERVED2

51

RESERVED3

RESERVED4

52

58

RESERVED5

RESERVED6

59

65

RESERVED7

RESERVED8

66

67

RESERVED9

42

LPS

91

87 LREQ

48

PD

86

PHYCTL0

85

PHYCTL1

PHYD0

82

PHYD1

81

PHYD2

80

PHYD3

79

PHYD4

76

PHYD5

75

PHYD6

74

PHYD7

73

49

RESERVED1

RESERVED10

68

71

8

H FD10

7

H FD11

4

H FD12

3

H FD13

2

H FD14

1

H FD15

10

HIFD8

9

HIFD9

HIFINTN

38

H FMUX

46

H FRDN

40

41

HIFWAIT

HIFWRN

37

ISON

93

92

LINKON

30

HIFA4

29

HIFA5

28

HIFA6

27

HIFA7

26

HIFA8

25

HIFAD0

22

HIFAD1

21

HIFAD2

20

19

HIFAD3

HIFAD4

16

HIFAD5

15

HIFAD6

14

HIFAD7

13

HIFALE

39

HIFCSN

36

119

131

137

11

17

23

34

43

53

60

69

HIF16BIT

45

HIFA0

33

HIFA1

32

HIFA2

31

HIFA3

121

AV2ERR1|DATAINV

122

AV2FSYNC

125

AV2READY

143

AV2SY

126

AV2SYNC

128

AV2VAL D

127

55

CLK50

CYCLEIN

56

CYCLEOUT

57

5

77

83

89

94

106

112

97

AV1FSYNC

100

AV1READY

118

101

AV1SY

103

AV1SYNC

AV1VALID

102

AV2CLK

124

AV2D0

133

AV2D1

134

AV2D2

135

AV2D3

136

AV2D4

139

AV2D5

140

141

AV2D6

AV2D7

142

AV2ENDPCK

123

AV2ERR0 LTLEND

1394MODE

47

AV1CLK

99

AV1D0

108

AV1D1

109

AV1D2

110

AV1D3

111

AV1D4

114

AV1D5

115

AV1D6

116

AV1D7

117

AV1ENDPCK

98

AV1ERR0

96

AV1ERR1

F121

PDI1394

7103

F120

2183

100n

F152

2148

100n

F124

F199

10K

3106

10K

3113

F109

F156

F162

3108

10R

47K

3101

3136

1R

F125

2177

100n

F122

6K34

3148

2158

1u

2155

100n

F143

F195

F170

F194

F169

F112

F141

47K

3118

47K

3127

F140

F187

F133

3179

10K

3180

10K

F105

F129

F148

10K

3102

3103

10K

2192

100n

47K

3192

F158

F110

3199

47K

F111

3189

10R

F123

F138

100n

2187

F139

47K

3198

2195

F119

100n

2178

100n

100n

2193

3109

47K

3104

47K

F144

3123

47K

F114

10R

3117

F103

5106

100MHZ

F142

F192

1394_RSTn

+3V3_IEEE_D

F104

+3V3_IEEE_D

+3V3_IEEE_A

+3V3_IEEE_D

+3V3_IEEE_A

PHY_CNA

+3V3_LINK

LINK_AVREADY

+3V3_LINK

PALE

LINK_CSn

LINK_INTn

PRDn

PWRn

+3V3_LINK

+3V3_LINK

+3V3_LINK

PA(0)

PA(1)

+3V3_IEEE_D

+3V3_LINK

+3V3_IEEE_D

PA(2)

PA(3)

PA(4)

PA(5)

PA(6)

PA(7)

PA(8)

PAD(0)

PAD(1)

PAD(2)

PAD(3)

PAD(4)

PAD(5)

PAD(6)

PAD(7)

PA(0:15)

{LINK_AVCLK,LINK_AVSYNC,LINK_AVVALID,LINK_AVFSYNC,LINK_CSn,LINK_INTn,LINK_AVREADY}

{SRAMCE0n,SRAMRDn,PINT0n,PINT1n,PALE,PWRn,PRDn,PRSTn}

+3V3_IEEE_PLL

+3V3_IEEE_D

+3V3_LINK

LINK_AVCLK

LINKFIFO DQ(1)

LINKFIFO DQ(2)

LINKFIFO DQ(3)

LINKFIFO DQ(4)

LINKFIFO DQ(5)

LINKFIFO DQ(6)

LINKFIFO DQ(7)

LINK AVFSYNC

LINK AVSYNC

LINK AVVALID

PAD(7:0)

LINKFIFO_DQ(7:0)

LINKFIFO DQ(0)

+3V3_LINK

+3V3

+3V3_IEEE_PLL

+3V3

+3V3

CL 16532145_014.eps

221101

1101

B1

1102

D1

2104

D3

2105

D3

2146

I5

2147

I5

2148

I6

2149

I6

2150

I6

2151

I6

2152

I6

2153

I7

2154

I7

2155

I7

2156

I7

2157

I8

2158

B2

2163

C2

2170

D1

2171

D1

2173

G3

2174

G4

2175

H3

2176

H3

2177

H3

2178

H4

2181

I2

2182

I3

2183

I3

2184

I3

2187

I4

2192

I8

2193

I8

2194

I8

2195

I8

2196

I9

2197

I9

3100

C13

3101

D13

3102

B13

3103

C12

3104

D13

3105

C7

3106

C12

3107

C7

3108

C7

3109

D13

3110

D13

3111

E8

3113

G9

3115

G14

3116

D2

3117

C7

3118

D13

3119

D13

3120

D13

3121

D13

3122

D13

3123

D13

3124

E12

3125

E12

3126

E12

3127

E12

3128

F12

3130

F12

3131

F12

3132

F12

3133

D13

3134

D13

3136

E3

3137

A8

3138

A7

3139

A7

3140

A8

3141

A8

3147

A3

3148

A3

3164

B2

3165

B2

3166

D8

3171

B7

3172

B7

3173

C2

3174

C7

3176

C7

3177

C2

3178

C2

3179

A7

3180

B7

3188

D7

3189

B7

3190

D7

3191

C7

3192

C13

3193

B7

3197

C13

3198

C13

3199

C13

4100

H12

4101

D7

4102

H12

4103

B13

5103

I5

5106

G2

5109

G2

5110

H2

7101

A5

7103

B12

F100

B8

F101

B8

F102

C8

F103

C8

F104

D8

F105

B8

F106

D8

F107

C8

F108

D7

F109

C6

F110

B6

F111

B6

F112

B6

F113

B6

F114

B6

F115

C6

F116

C6

F117

E7

F118

B2

F119

B2

F120

C2

F121

C2

F122

B2

F123

C2

F124

B12

F125

B12

F126

B9

F127

B12

F128

B12

F129

B12

F130

B12

F131

B12

F132

B12

F133

B12

F134

C12

F135

C12

F136

C12

F137

E4

F138

G4

F139

G4

F140

H4

F141

I9

F142

C6

F143

C12

F144

C12

F146

D1

F148

A3

F149

C6

F150

B3

F152

C6

F153

C8

F154

C8

F156

C8

F157

C6

F158

C8

F161

D12

F162

D1

F163

C12

F165

C12

F166

C12

F167

C12

F168

C12

F169

D12

F170

D12

F171

D12

F172

D12

F174

G12

F175

D8

F184

D12

F185

D2

F186

D12

F187

D12

F188

D12

F189

D12

F190

D12

F191

D12

F192

E3

F193

E3

F194

B6

F195

A8

F197

B13

F198

G12

F199

B1

F601

A6

F602

B9

Summary of Contents for DVDR880/001

Page 48: ...Mechanical Instructions EN 50 DVDR880 890 0X1 4 4 5 Dismantling Instructions Figure 4 14 ...

Page 166: ...Circuit IC Descriptions and List of Abbreviations EN 168 DVDR880 890 0X1 9 ...

Page 167: ...Circuit IC Descriptions and List of Abbreviations EN 169 DVDR880 890 0X1 9 ...

Page 174: ...Circuit IC Descriptions and List of Abbreviations EN 176 DVDR880 890 0X1 9 IC7411 ...

Page 182: ...Circuit IC Descriptions and List of Abbreviations EN 184 DVDR880 890 0X1 9 ...

Page 183: ...Circuit IC Descriptions and List of Abbreviations EN 185 DVDR880 890 0X1 9 ...

Page 184: ...Circuit IC Descriptions and List of Abbreviations EN 186 DVDR880 890 0X1 9 ...

Page 203: ...Circuit IC Descriptions and List of Abbreviations EN 205 DVDR880 890 0X1 9 ...