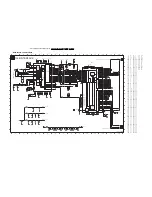

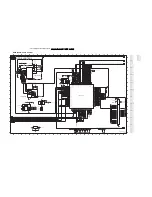

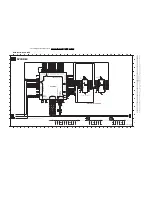

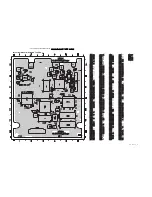

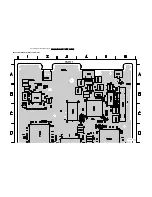

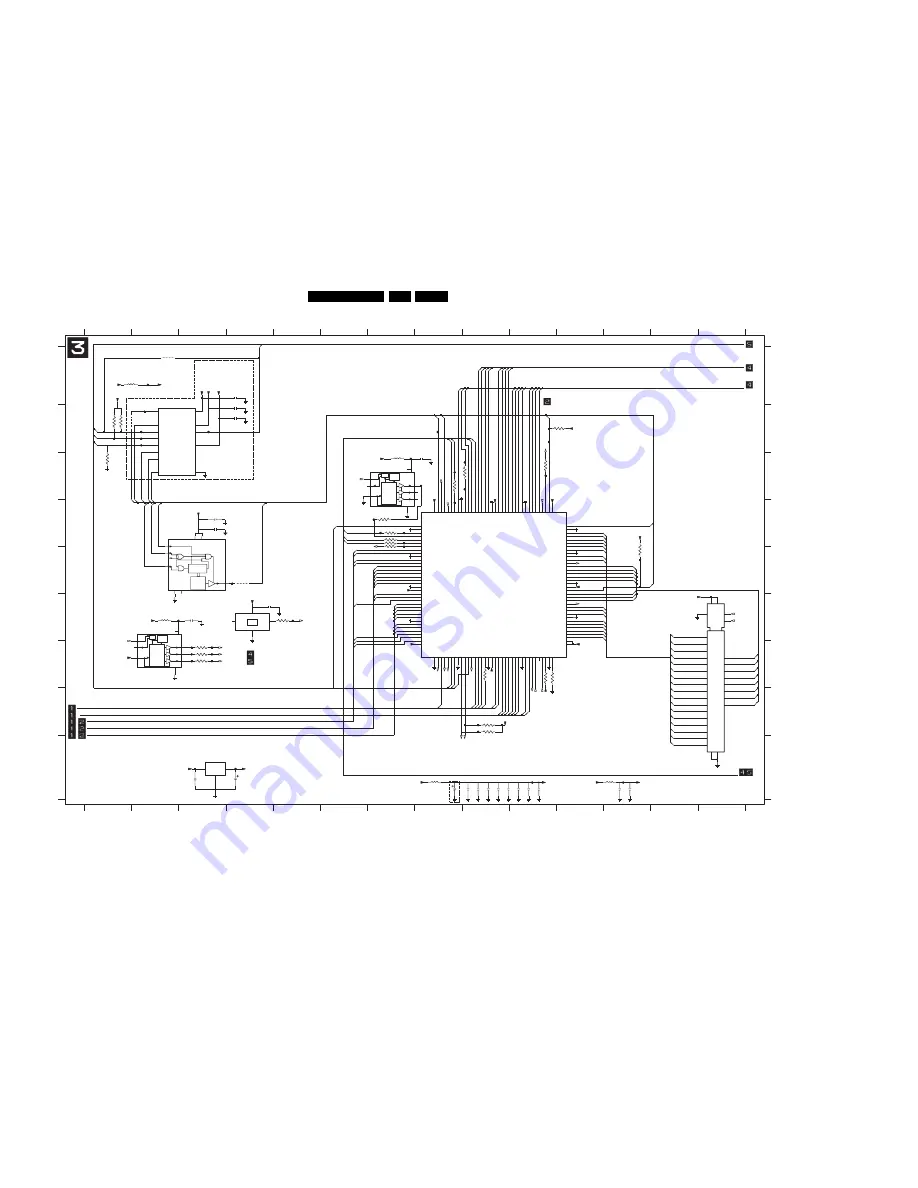

Circuit Diagrams and PWB Layouts

EN 121

DVDR880-890 /0X1

7.

DVIO Board: Fifo & Control

VCC

CELL

MATRIX

COUNTER

EPROM

ADDR

BLOCK

OSC

MULT

PLEXER

AND DIV

DE

LOGIC

CONF

GURABLE

PLL

EPROM

BLOCK

OSC

MULTIPLEXER

AND DIVIDE

LOGIC

CONFIGURABLE

PLL

EPROM

OSC

VCC

GND

AUD SDO DAC

AUD

SDO

CON

TDI

TCK

TMS

CCLK

PROGRAMn

{DATA,CCLK,DONE,INITn,PROGRAMn}

{TDI,TCK,TDO,TDO CONF,TMS}

TDO_CONF

PA(8:15)

+3V3_FPGA

CONFIG FLASH

CONFIG ROM

PLL VIDEO

PLL AUDIO

11

12

13

3

4

5

6

7

12

2

3

4

5

6

FIFO & CONTROL

FPGA / EPLD

SRAM

F

G

H

I

A

B

C

D

E

D

E

F

G

H

I

14

A

B

C

8

9

10

OPTION

OPTION

13

14

1

2

7

8

9

10

11

1

F316

F322

F319

F326

47u

2314

3331

47R

4302

F310

3330

47R

F309

F301

F302

2332

100n

4300

F333

F335

F336

2330

100n

2331

100n

15

16

16

17

17

18

18

19

19

2

2

20

20

3

3

4

4

5

5

6

6

7

7

8

8

9

9

XC18V01

7309

1

1

10

10

11

11

12

12

13

13

14

14

15

10K

3328

3329

10K

4301

VCC2

37

VCC3

54

VCC4

73

VCC5

90

VCC6

108

VCC7

128

144

VCC8

I|O91

117

I|O92

119

I|O93

120

I|O94

121

I|O95

122

123

I|O96

I|O97

124

I|O98

125

I|O99

126

M0

36

M1

34

O TDO

109

74

PROGRAM_

PWRDWN

38

VCC1

18

I|O77

98

I|O78

99

I|O79-D1

101

I|O8

10

I|O80

102

I|O81

103

I|O82

104

I|O83-D0-D

N

105

I|O84-GCK6-DOUT

106

I|O85

111

I|O86 GCK7

112

I|O87

113

114

I|O88

I|O89 CS1

115

I|O9-TMS

11

I|O90

116

I|O62

80

I|O63

82

I|O64

83

I|O65-D5

84

I|O66

85

I|O67

86

I|O68

87

I|O69-D4

88

I|O7

9

I|O70

89

I|O71-D3

92

I|O72

93

94

I|O73

I|O74

95

I|O75-D2

96

I|O76

97

I|O48

61

I|O49

62

I|O5-TDI

6

I|O50

63

I|O51

65

I|O52

66

I|O53

67

I|O54

68

I|O55

69

I|O56 GCK4

70

I|O57-D7

75

I

O58-GCK5

76

77

I|O59

I|O6-TCK

7

I|O60

78

I|O61-D6

79

I|O33

43

I|O34 LDC

44

I|O35

46

I|O36

47

I|O37

48

I|O38

49

I|O39

50

I|O4

5

I|O40

51

I|O41

52

I O42 INIT

53

I|O43

56

57

I|O44

I|O45

58

I|O46

59

I|O47

60

I|O19

23

I|O2

3

I|O20

24

I|O21

25

I|O22

26

I|O23

28

I|O24

29

I|O25

30

I|O26

31

32

I|O27

I|O28-GCK2

33

I|O29 GCK3

39

4

I|O3

I O30 HDC

40

I|O31

41

I|O32

42

I|O106

135

I|O107

136

I|O108

138

I|O109

139

I|O11

13

I|O110

140

I|O111

141

I|O112

142

I|O113 GCK8

143

14

I|O12

I|O13

15

16

I|O14

19

I|O15

I|O16

20

I|O17

21

I|O18

22

GND2

8

GND3

17

GND4

27

GND5

35

GND6

45

GND7

55

GND8

64

GND9

71

I|O1-GCK1

2

12

I|O10

I|O100

129

130

I|O101

131

I|O102

I|O103

132

I|O104

133

I|O105

134

7303

XCS30XL

CCLK

107

DONE

72

GND1

1

81

GND10

GND11

91

GND12

100

110

GND13

GND14

118

127

GND15

GND16

137

F330

F331

F332

3327

47R

GND

5

NC

6

RESET|OE_

3

7

8

F329

7300

XC17S30XL

CE_

4

CLK

2

DATA 1

47R

3321

47R

3322

47R

3325

3312

10R

47R

3320

F328

F314

F317

F315

F321

F318

F323

F324

F325

F320

F303

5300

100MHZ

6300

LD1117

GND

1

IN

3

OUT

2

100n

2304

F300

47u

2302

2305

100n

100n

2301

CLKB 5

6

CLKC

2

GND

OE|FS

8

7

VDD

3

XTI

4 XTO

100MHZ

5301

3315

CY2071AS

7307

1

CLKA

33R

3318

33R

3319

33R

3317

33R

F305

F308

F307

1

VDD

4

F306

7304

FXO-31FT

GND

2

OUT

3

TS

2303

100n

CY2071AS

7308

CLKA 1

5

CLKB

6

CLKC

2

GND

8 OE|FS

7

VDD

3 XTI

4 XTO

3305

1K

F311

F313

F312

F304

3313

10K

10K

3314

5303

100MHZ

100MHZ

5302

3303

1K

1K

3306

3301

1K

1K

3307

2312

100n

100n

2313

100n

5304

100MHZ

2324

10R

3300

100n

2325

100n

2319

100n

2306

2309

100n

2307

100n

100n

2308

2311

100n

100n

2310

WE_

2318

100n

A8

A9

18

CE_

5

9

25

I|O0

6

I|O1

7

I|O2

10

I|O3

11

I|O4

22

I|O5

23

I|O6

26

I|O7

27

OE_

28

8

24

12

1

A1

2

A10

19

20

A11

A12

21

29

A13

A14

30

31

A15

32

A16

A2

3

A3

4

13

A4

A5

14

15

A6

16

A7

17

7301

CY7C1019BV33-10VC

A0

LINK

AVREADY

+3V3_FPGA

CCLK

+3V3_FPGA_CONF

+3V3_FPGA_CONF

DATA

+3V3_FPGA_CONF

+3V3_FPGA_CONF

PROGRAMn

+3V3_FPGA

INITn

INITn

+3V3_FPGA

DONE

INITn

CCLK

DATA

DOUT

IO1

IO3

IO4

IO10

{AUD_BCLK,AUD_WS_OUT,AUD_WS_701,AUD_MUTE,AUD_SDI,AUD_SDO_DAC,AUD_SDO_CON}

DV_HS_IN

DV_HS_OUT

HAD(7)

HAD(6)

HAD(5)

HAD(4)

HAD(3)

HAD(2)

HAD(1)

HAD(0)

DV

LCn

DV_ERRn

DV

DRQn

DV_DTACKn

DV

RSTn

DV_RWn

DV

DSUn

DV_DSLn

CLK27M

HAD(7:0)

{DV_LCn,DV_ERRn,DV_DRQn,DV_DTACKn,DV_ASn,DV_PDn,DV_DSUn,DV_RWn,DV_VS,DV_HS_IN,DV_RSTn,DV_HS_OUT,DV_DSLn}

FIFOA_D(7:0)

+3V3_FPGA_CONF

CLK27M_OSC

DONE

{LINK_CYCLEOUT,LINK_AVCLK,LINK_AVSYNC,LINK_AVVALID,LINK_AVFSYNC,LINK_AVERR1,LINK_AVERR0,LINK_CSn,LINK_INTn,LINK_AVREADY}

AUD_WS_OUT

PAD(0)

PAD(1)

PAD(2)

PAD(3)

PAD(4)

PAD(5)

PAD(6)

PAD(7)

PAD(7:0)

PA(8)

PA(9)

PA(10)

PA(11)

PA(12)

PA(13)

PA(14)

PA(15)

TDO

SRAMCE0n

SRAMRDn

PWRn

PRDn

PRSTn

PINT0n

PINT1n

PALE

{SRAMCE0n,SRAMRDn,PINT0n,PINT1n,PALE,PWRn,PRDn,PRSTn}

LINKFIFO

DQ(4)

LINKFIFO

DQ(5)

LINKFIFO_DQ(0:7)

LINKFIFO_DQ(6)

LINKFIFO

DQ(7)

LINK

AVVALID

LINK_AVSYNC

LINK

AVCLK

LINK

AVFSYNC

LINK_INTn

LINK_CSn

TDO

CONF

TCK

TMS

+3V3

BUFENn_AUD

BUFENn_VID

AUD BCLK

FIFOA_D(4)

FIFOA D(3)

FIFOA D(5)

FIFOA_D(0)

FIFOA_D(7)

FIFOA_D(1)

FIFOA_D(6)

FIFOA_D(2)

FIFOA_A(16:0)

DONE

DATA

AUD_MUTE

AUD_SDI

AUD

WS

701

DV

ASn

CLK27M_OSC

PHY_CNA

1394_RSTn

LINKFIFO

DQ(0)

LINKFIFO

DQ(1)

LINKFIFO

DQ(2)

LINKFIFO_DQ(3)

RESETn

+3V3_SRAM

+3V3_FPGA

+3V3_FPGA

+3V3_FPGA

+3V3_FPGA

+3V3_FPGA

+3V3_FPGA

+3V3_FPGA

FIFOA_A(0)

FIFOA_A(16)

FIFOA_A(1)

FIFOA_A(15)

FIFOA_A(2)

FIFOA_A(14)

FIFOA_A(3)

FIFOA_A(13)

FIFOA_A(8)

FIFOA_A(7)

FIFOA_A(9)

FIFOA_A(6)

FIFOA_A(10)

FIFOA_A(5)

FIFOA_A(11)

FIFOA_A(4)

FIFOA_A(12)

+3V3

CLOCKGENAUD

+5V_PROC

CLK27M_DV

CLK27M_CON

+3V3

CLOCKGENVID

+3V3_PLL

+3V3_PLL

+5V

+3V3_PLL

CLOCKGENAUD

CLOCKGENVID

CLK27M

FIFOA_WEn

FIFOA_OEn

FIFOA_A(0)

FIFOA_A(1)

FIFOA_A(10)

FIFOA_A(11)

FIFOA_A(12)

FIFOA_A(13)

FIFOA_A(14)

FIFOA_A(15)

FIFOA_A(16)

FIFOA_A(2)

FIFOA_A(3)

FIFOA_A(4)

FIFOA_A(5)

FIFOA_A(6)

FIFOA_A(7)

FIFOA_A(8)

FIFOA_A(9)

FIFOA_D(0)

FIFOA_D(1)

FIFOA_D(2)

FIFOA_D(3)

FIFOA_D(4)

FIFOA_D(5)

FIFOA_D(6)

FIFOA_D(7)

FIFOA_OEn

+3V3_SRAM

FIFOA_WEn

+3V3_FPGA

+3V3_FPGA_CONF

+3V3

+3V3

CL 16532145_016.eps

221101

2301 I3

2302 I4

2303 F4

2304 C8

2305 F3

2306 I9

2307 I9

2308 I9

2309 I9

2310 I9

2311 I10

2312 I10

2313 I10

2314 I8

2318 D3

2319 D3

2324 I12

2325 I12

2330 A4

2331 B4

2332 B4

3300 G9

3301 B11

3303 E12

3305 B1

3306 B1

3307 C1

3312 F5

3313 H9

3314 H9

3315 D7

3317 G3

3318 G3

3319 G3

3320 D7

3321 D7

3322 C10

3325 D7

3327 C9

3328 G10

3329 G11

3330 C8

3331 D7

4300 B1

4301 E4

4302 A2

5300 C7

5301 F2

5302 I8

5303 A1

5304 I12

6300 I3

7300 D2

7301 F13

7303 D10

7304 F4

7307 C7

7308 F2

7309 A2

F300 F5

F301 C8

F302 C8

F303 D7

F304 D7

F305 G3

F306 C10

F307 G3

F308 G3

F309 D7

F310 D7

F311 I10

F312 A2

F313 I12

F314 C7

F315 C8

F316 B2

F317 F2

F318 H9

F319 B2

F320 H9

F321 G3

F322 B2

F323 G3

F324 B2

F325 I4

F326 B3

F328 E4

F329 G3

F330 D7

F331 C8

F332 C8

F333 E12

F335 B10

F336 B8

Summary of Contents for DVDR880/001

Page 48: ...Mechanical Instructions EN 50 DVDR880 890 0X1 4 4 5 Dismantling Instructions Figure 4 14 ...

Page 166: ...Circuit IC Descriptions and List of Abbreviations EN 168 DVDR880 890 0X1 9 ...

Page 167: ...Circuit IC Descriptions and List of Abbreviations EN 169 DVDR880 890 0X1 9 ...

Page 174: ...Circuit IC Descriptions and List of Abbreviations EN 176 DVDR880 890 0X1 9 IC7411 ...

Page 182: ...Circuit IC Descriptions and List of Abbreviations EN 184 DVDR880 890 0X1 9 ...

Page 183: ...Circuit IC Descriptions and List of Abbreviations EN 185 DVDR880 890 0X1 9 ...

Page 184: ...Circuit IC Descriptions and List of Abbreviations EN 186 DVDR880 890 0X1 9 ...

Page 203: ...Circuit IC Descriptions and List of Abbreviations EN 205 DVDR880 890 0X1 9 ...