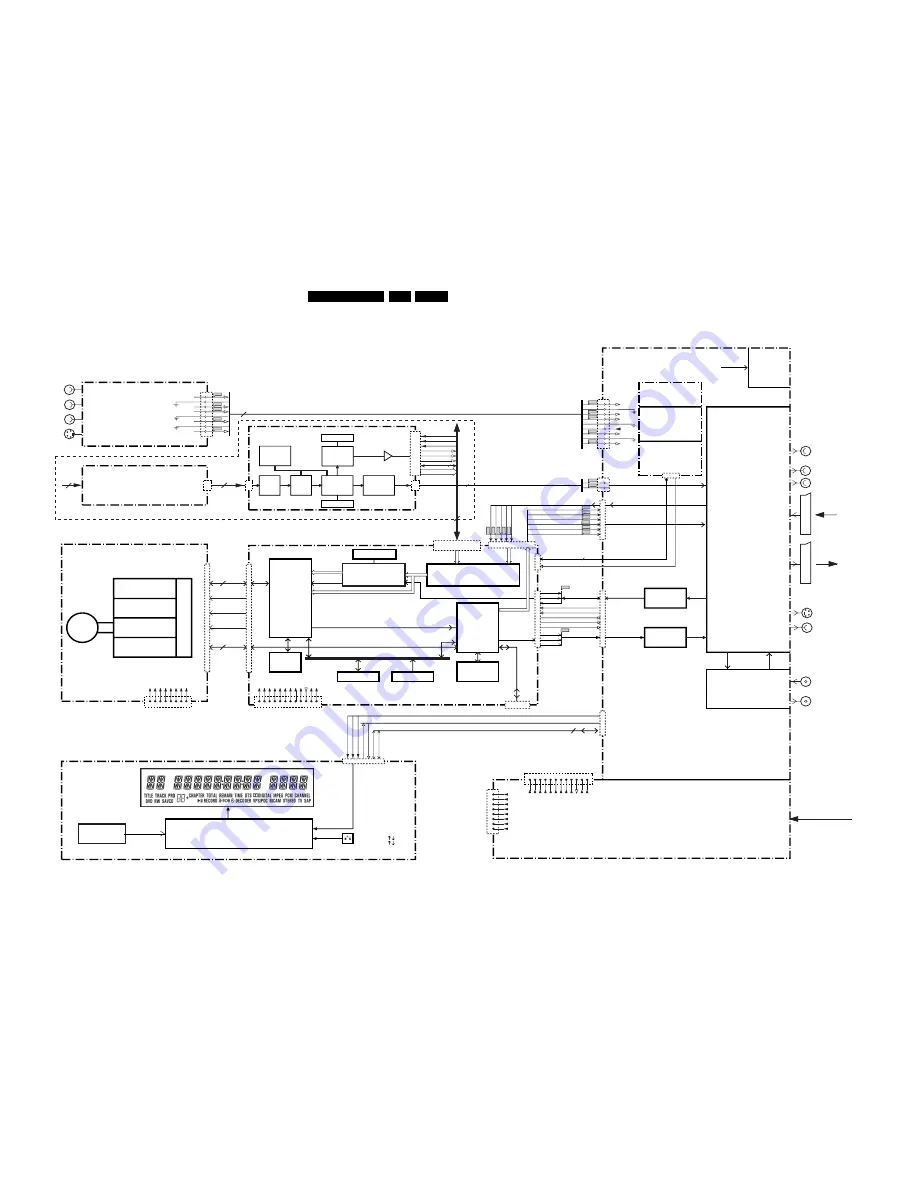

Block Diagrams, Waveforms, Wiring Diagram.

EN 81

DVDR880-890 /0X1

6.

6.

Block Diagrams, Waveforms, Wiring Diagram.

BLOCK DIAGRAM DVDR880, DVDR890 EURO

FRONT

Analog input

FRONT

Digital Video input

IEEE 1394

4

DIGITAL PCB 1.5

VSM

Stream

Manager

SDRAM

MPEG VIDEO

ENCODING

EMPRESS

SDRAM

FLASH 4MB

DRAM

VIDEO INPUT

PROCESSING

MPEG

AV

DECODER

+ HOST

(Sti5508)

2MB

SDRAM

ANAL.VIDEO

DIG. AUDIO

VSM_UART1

IRESET_DIG

CVBS-RGB-Y/C

RS232

SERVICE

AUDIO PCM I2S

SPDIF

AE_WCLK

AE_BCLK

AD_DATAI

OPT_IN

COAX_IN

MUTEN

AD_ACLK

AUDIO ENCODER I2S

YUV-YCVBS/C

ANALOG AUDIO L/R

ANALOG AUDIO VIDEO

DVIO 1.5

PHY

LINK

FPGA

SRAM

BE_FAN

+3V3

CVBS_OUT_B

C_OUT_B

Y_OUT_B

R_OUT_B

G_OUT_B

B_OUT_B

V_IN

U_IN

Y_IN

C_IN

CVBS_Y_IN

+5V

RESETN_BE

BE_LOADN

S2B

S2B

I2S

FRONT-END I2S

FRONT-END I2S or //

DRAM

8051

4

9

DV CODEC

AUDIO DAC

(D

A

T

A+CONTR

OL+PSU)

DVD & RW ENGINE

TRAY CONTROL

SERVO

READ

WRITE

DISC

PSU

INFRA RED

EYE

DISPLAY & CONTROL

PSU

IPOR_DC

I2C

2

CLOCK &

BACKUP

TUNER

INPUT/OUTPUT

PROCESSING &

SOURCE

SELECTION

DAC

CONTROL

uP

P50

FAN

12V

DC

OPTIONAL

INTELLIGENT

CONTROL

ANALOG BOARD

MAINS

AC

S-VIDEO

SCART II

AUX-

I/O

SCARTI

TO TV

- I/O

CVBS

AUDIO DIGITAL

DIGITAL PCB

ENGINE

7

DATA

&CONTROL

LASER

EMI BUS

1933

1932

1

1

2

3

4

5

6

7

2

3

4

5

6

7

8

+3V3

+3V3

+3V3

+3V3

GND

GND

+5V

+12V

GND

GND

-5V

ION

+12Vstb

y

-Vgnstb

y

SCL

SD

A

INT

POR_DC

5STBY

9

10 11 12

A1

A1

V1

V2

V3

A1

A2

A2

A3

A4

A1

V1

V2

V3

V9

V4

V5

V6

V7

V8

V10

V11

V12

V13

V14

2

1

AFCRI

AFCLI

CVBSFIN

CFIN

YFIN

3

4

5

7

8

9

8

1900

1402

1911

1001

1101

1500

1953

1960

1947

1986

1900

1943

1903

1916

4

2

8

5

3

9 10

1602

1600

1601

1501

4

1501

1902

1

2

3

4

5

6

7

+3V3

+5V

GND

GND

GND

+4V6E

-5V

+12V

8

PSU

1

2

3

4

5

6

7

+3V3

+3V3

+3V3

+3V3

GND

GND

GND

ION

+5V

+12V

8

1

1000

9

10 11

GND

-5V

12

S-VIDEO

CVBS

AUDIO R

AUDIO L

AFCRI

ANA_R

ANA_L

AFCLI

CVBSFIN

8SW

CFIN

YFIN

AUDIO L/R

5

+12V

DV_HS_OUT

DV_VS

DV_CLK

VSM_UART2

YUV(7:0)

4

4

60

ANTENNA INPUT

TV OUT

ADC

DIG.VIDEO

VIDEO MPEG2

AUDIO MPEG1

1

2

3

4

5

6

7

8

9

1

4

12

14

16

18

20

22

1

10

20

21

18

2

4

3

7

9

11

12

14

22 20 18 16 14

+3V3

+5V

GND

GND

GND

+4V6E

5V

+12V

POWER

OPEN/CLOSE

PLAY

STOP

RECORD

REC-MODE

CHANNEL

TRACK

FRONT PROCESSOR

AD_DATAO

AD_WCLK

AD BCLK

NOT USED IN DVDR 880

uP SUB BOARD

MULTI-MODE SOPS

10

TR 01018_001

130502

Summary of Contents for DVDR880/001

Page 48: ...Mechanical Instructions EN 50 DVDR880 890 0X1 4 4 5 Dismantling Instructions Figure 4 14 ...

Page 166: ...Circuit IC Descriptions and List of Abbreviations EN 168 DVDR880 890 0X1 9 ...

Page 167: ...Circuit IC Descriptions and List of Abbreviations EN 169 DVDR880 890 0X1 9 ...

Page 174: ...Circuit IC Descriptions and List of Abbreviations EN 176 DVDR880 890 0X1 9 IC7411 ...

Page 182: ...Circuit IC Descriptions and List of Abbreviations EN 184 DVDR880 890 0X1 9 ...

Page 183: ...Circuit IC Descriptions and List of Abbreviations EN 185 DVDR880 890 0X1 9 ...

Page 184: ...Circuit IC Descriptions and List of Abbreviations EN 186 DVDR880 890 0X1 9 ...

Page 203: ...Circuit IC Descriptions and List of Abbreviations EN 205 DVDR880 890 0X1 9 ...