Service Modes, Error Codes, and Fault Finding

5.

There are several types of protections:

•

I

2

C related protections.

•

OTC related protections (via polling on I/O pins or via

algorithms).

•

HOP related protections (mainly for deflection items).

•

Hardware errors that are not sensed by the OTC (e.g.

vertical flyback protection, bridge coil protection, E/W

protection, arcing protection).

All protections are explained below.

5.7.2

I

2

C Related Protections

In normal operation, some registers of the I

2

C controlled ICs

are refreshed every 200 ms. During this sequence, the I

2

C

busses and the I

2

C ICs are checked.

An I

2

C protection will take place if the SDA and SCL lines are

short-circuited to ground, or to each other. An I

2

C error will also

occur, if the power supply of the IC is missing (e.g. FBX_PROT

(error 16)).

5.7.3

OTC Related Protections

If a protection is detected at an OTC input, the OTC will start to

scan all protection inputs every 200 ms for 5 times. If the

protection on one of the inputs is still active after 1 s, the

microprocessor will put the set in the protection mode. Before

the scanning is started, a so-called “ESD refresh” is carried out.

This is done, because the interrupt on one of the inputs is

possibly caused either by a flash or by ESD. As a flash or ESD

can influence IC settings, the HIP, MSP, 3D Comb (US only)

and wireless module are initialised again, to ensure the normal

picture and sound conditions of the set.

8 V and 5 V protections: The microprocessor senses the

presence of the 8 V and 5 V (via the “+5V_CON” and

“+8V_CON” lines). If one (or both) of these voltages is (are) not

present, an error code is stored in the error buffer of the NVM,

and the set is put in the protection mode.

5.7.4

HOP Related Protections

The OTC reads every 200 ms, the status register of the HOP

(via the I

2

C bus). If a protection signal is detected on one of the

inputs of the HOP, the relevant error bit in the HOP register is

set to “high”. If this error bit is still “high” after 1 s, the OTC will

store the error code in the error buffer of the NVM and,

depending on the relevancy of the error bit, the set will either

go into the protection mode or not.

The following protections are implemented:

•

HFB (Horizontal Flyback): If the horizontal flyback is not

present, this is detected via the HOP

(HFB_X-RAY_PROT). One status bit is set to “high”. The

error code is stored in the error buffer and the set will go

into the protection mode.

•

XPR (X-ray protection): If the HFB pulses are too low

(level detection), the HOP will detect this via the XPR-bit.

The error will be logged in the error buffer and the set will

go into protection mode.

Note: Both errors will be logged as HFB-failure.

5.7.5

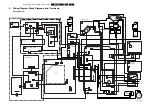

Hardware Related Protections

Due to the architecture (“hot” deflection), some protections

cannot be sensed by the microprocessor. Three of these

protections will lead to a protection on set level (Standby mode

and blinking LED), while another will only lead to a circuit

protection.

TV-set Protection

The following fault conditions will lead to a “complete” set

protection:

•

BRIDGECOIL protection: This is sensed via the “EW”

signal going to the base of TS7652 (via R3495 and D6499).

In a normal situation, the voltage on C2498 (diagram A4) is

high and TS7652 is conducting. When bridge coil 5422

(diagram A3) is short circuited, the voltage on C2498

changes to low, which will block TS7652. In this case, also

TS7641 will block and the voltage on 2642 will rise until

TS7443 is forced in conduction. The “SUP-ENABLE” signal

(in normal operating condition -20 V) is shorted now to

ground level, which will force the Main Power Supply to

Standby mode.

•

ARC protection: If there are “open” connections (e.g. bad

solder joints) in the high-energy deflection circuitry, this can

lead to damaging effects (read: fire). For that reason, the E/

W current is sensed (via 3479//3480). If this current

becomes too high, the “thyristor” circuit (TS7653 and

TS7654) is triggered. TS7442 is switched “on” and TS7443

is forced into conduction. . The “SUP-ENABLE” signal is

shorted now to ground level, which will force the Main

Power Supply to Standby mode.

•

NON_VFB (No vertical Flyback) protection: If the frame

stage generates no pulses, TS7641 will block. TS7443 is

now switched “on”, which will lead to Standby mode.

Therefore, in normal operation condition, TS7641 and

TS7652 are conducting, while TS7443 is blocked.

Circuit Protection

The following fault condition will lead to a “partly” set protection:

•

PROT1 (DC) protection: When a DC-voltage (positive or

negative) is sensed on one of the loudspeaker outputs, the

protection circuit (TS7704, 7705, 7706 and 7707 in

diagram A6) will put the IC7700 in Standby mode (via tri-

state input pin 6). For more details, see chapter “Circuit

Descriptions”.

5.8

Repair tips

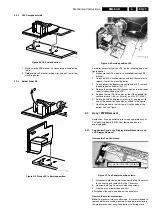

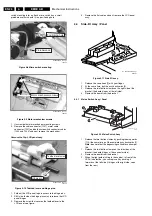

5.8.1

Miscellaneous

The relay you hear when you switch the set “on” (from Standby

or via the mains switch), is from the degaussing circuitry. It is

not used for switching the Power Supply (as done in the MG-

chassis).

Take care not to touch the “hot” heatsink while disconnecting

the SSP, despite the fact that the mains cord is out of the mains

socket. There can still be an annoying rest-voltage on the

heatsink for a short while. Because the discharge resistors

3502 and 3503 (on the LSP between hot and cold part) are not

stuffed for Europe. Instead, discharge resistors 3066 and 3057

on the Mains Switch panel are used, but because they are

located before the Mains switch, they only discharge when this

switch is “on”.

Advice: when you want to disconnect the SSP, first disconnect

the Mains cord, but keep the Mains Switch “on”.

Where the circuitry was too “crowded” for service printing, you

can find the correct location on the “test point overviews” in this

manual.

A very large part of the LSP is “hot”, such as:

–

The primary part of the Standby Supply.

–

The whole Main supply (except for the secondary Audio

supply).

–

And the complete deflection circuitry (so notice that the

deflection coil is hot!).