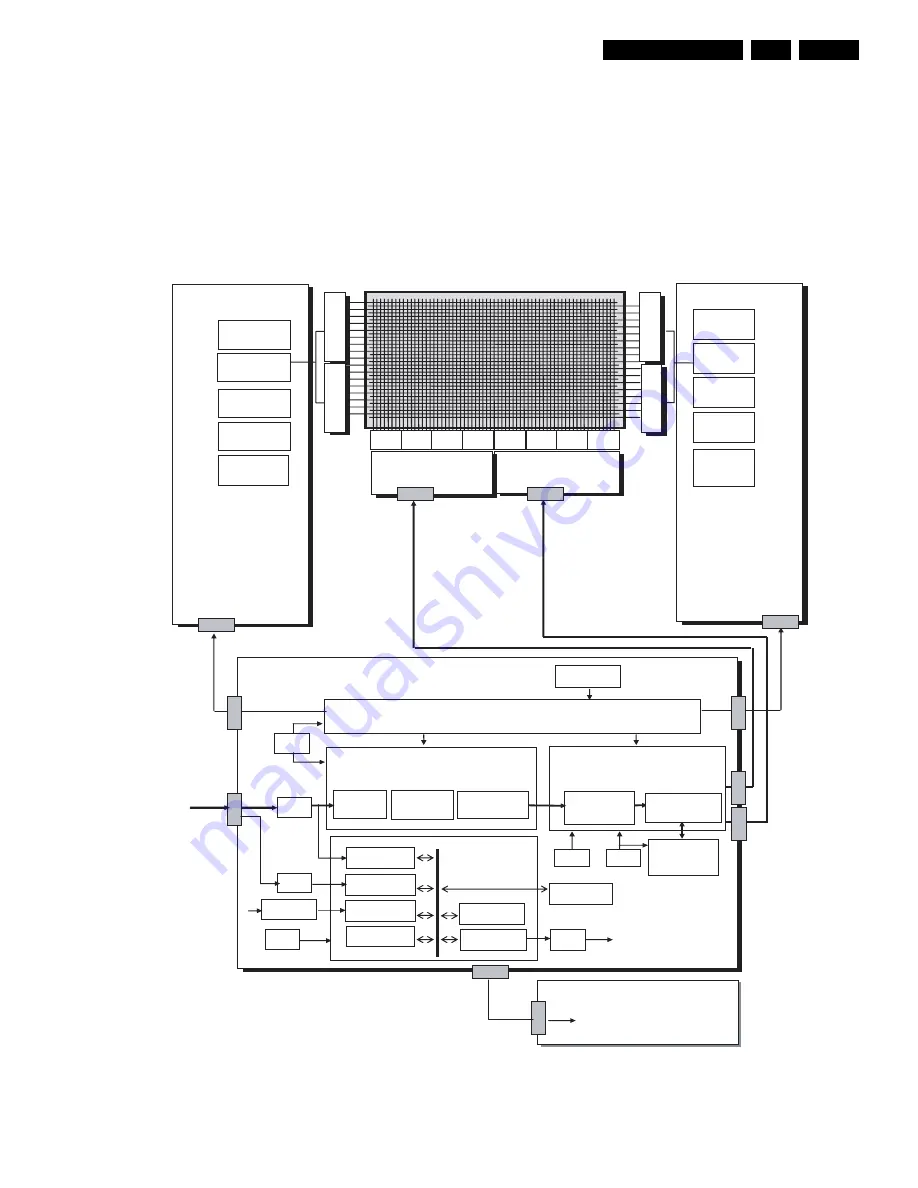

Block Diagrams, Test point Overview, and Waveforms

EN 33

FHP PDP

6.

6.

Block Diagrams, Test point Overview, and Waveforms

6.1

Block Diagrams

Figure 6-1 Signal block diagram

E_14580_003.eps

300905

PFCgo

Vsago

Vcego

CN69

CN7

PSU B.

*1

DATA CONVERTER

Y-SCAN

EVEN SW

X-SCAN

EVEN SW

ABUSR B.

ABUSL B.

X

B

B

X

B

B

S

D

M

S

D

M

SCAN CONTROLLER

FRAME

MEMORY

DATA PROCESSOR

OSC

TIMING ROM

γ

comp.

OSC

80MH

MPU

OSC

10MHz

Y-SUS B.

X-SUS B.

LOGIC B.

Y-SUS

EVEN SW

X-SUS

EVEN SW

CN31

Y-SUS

ODD SW

Y-SCAN

ODD SW

X-SUS

ODD SW

X-SCAN

ODD SW

RGB

GAIN

DITHER

/ERR

SUB FIELD

PRC.

POS

RESET SW

POS /NEG

RESET SW

MEMORY

CONTROLLER

ADM1

ADM4

ADM8

ADM7

ADM6

ADM5

ADM3

ADM2

LVDS

24MHz

SIGNAL

INPUT

Vrs

Vra

Vrw

Vrx

D/A

V-SYNC cont

.

APC cont

.

I/O

EEPROM

Failure DET.

FLASH

Analog Sw

OSC

40MH

CN1

CN3

CN2

CN21

SCI.

I

2

C

CN5

CN41

CN51

*1:Power supply(jig)

CN4