10-9

10-9

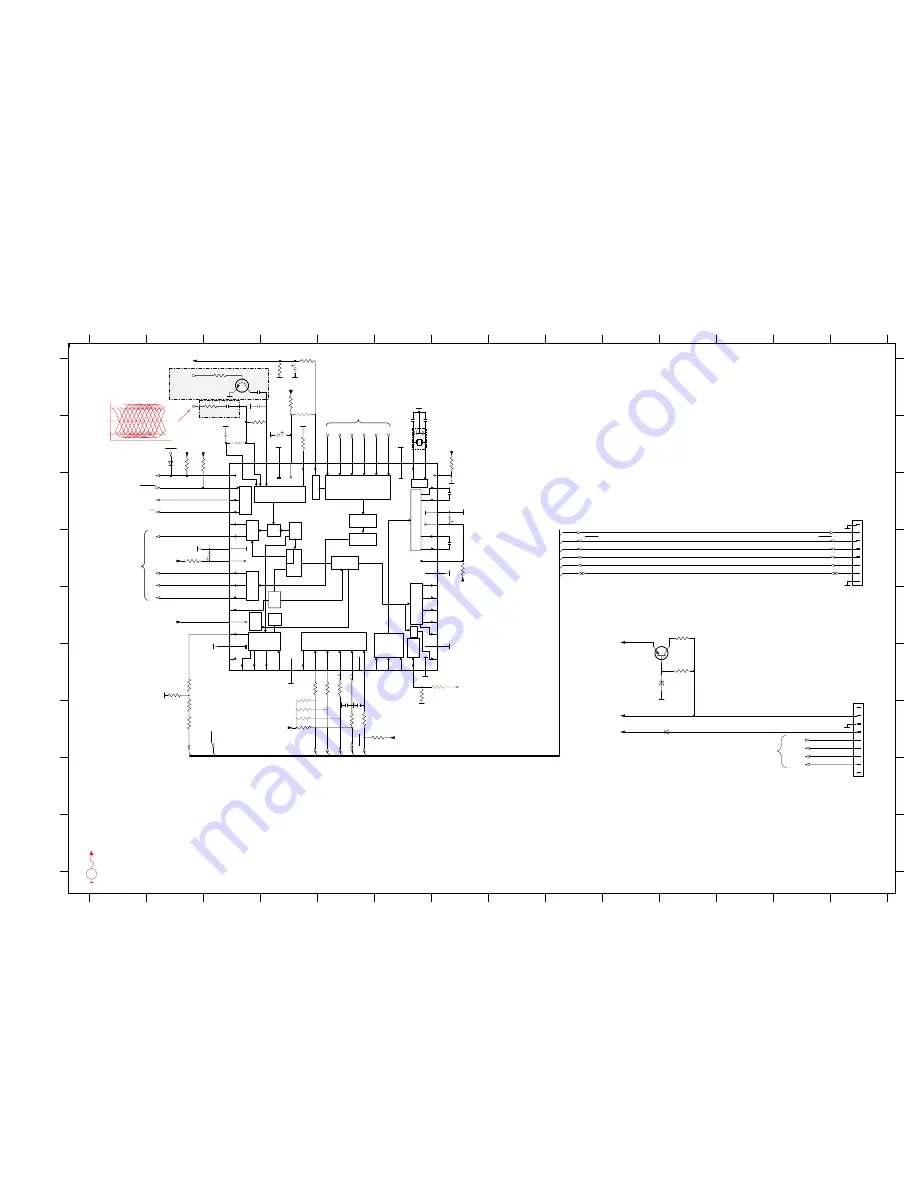

voltage stab.

100R

3769

6807

BZX284

C3V9

6811

1N4003

3767

33R

BC847B

7815

+5V

SW_INFO

+10V

SHR_CL

SHR_DATA

SHR_STR

+3.3V

3CDC-LC

part 2

comm

unication with

Shift Register

on par

t 3

comm

unication with

F

ront microprocessor

KILL

TIMING

BITSTREAM D

A

C

SER.

D

A

T

A

INTERF

A

CE

VERSA

T

.

INTERF

.

EB

U

INTERF

.

CORR.

ERR

OR

CONTROL

FUNCTION

PRE-

PROCESSING

AUDIO

PROCESSOR

MICROCONTROLLER

INTERFACE

SUBCODE

PROCESSOR

ADDR

SRAM

PEAK

DET.

M

OTO

R

CONTR

OL

OUTPUT

ST

A

GES

DIG.

PLL

EFM

DEMOD

VERSA

TILE

INTERF

A

CE

ANALOG / DIGITAL

CONVERTER

VREF GEN.

FRONTEND

for 4x:

2823 = 22p

from part1 1801

to 6812

Signal Processor

4

VSSA2

14

VSSD1

33

VSSD2

50

VSSD3

58

WCLI

35

WCLK

28

SUB

46

TEST1

25

TEST2

31

TEST3

44

V1

63

V2|V3

34

V4

61

V5

62

VDD

A1

5

VDD

A2

17

VDDD1P

52

VDDD2C

57

VNEG

20

VPOS

21

VRIN

7

VSSA1

RAB

RCK

45

RESET

38

RN

22

RP

23

SBSY

48

SCL

40

SCLI

37

SCLK

29

SD

A

39

SDI

36

SELPLL

24

SFSY

47

SILD

42

56

SL

ST

A

TUS

43

FO

55

HFIN

2

HFREF

1

IREF

6

ISLICE

3

KILL

32

LDON

64

LN

18

LP

19

MOTO1

59

MOTO2

60

R1

12

R2

13

RA

54

41

SAA7324/SAA7325

CFLG

53

CL11|4

49

CL16

26

CRIN

16

CR

OUT

15

D1

8

D2

9

D3

10

D4

R1

R2

D1

D2

D3

D4

11

DATA

27

DOEM

51

30

EF

7802

10K (4x)

3819

470R

470R

2843

100n

+3.3V

3865

120R

22K

3828

3810

470R

15R

3855

+3.3V

2826

47u

2823

47p

120R

3862

AT-49

1810

2818

1n5

2833

33p

+3.3V

10K

3809

+3.3V

PORE

+3.3V

3812

470R

27p

2829

1n

2820

33p

3804

10K

+3.3V

3832

10K

1n5

2816

470R

27K

3827

+3servo

4u7

Innersw

LDON

RAB

SD

A

PORE

SICL

SILD

SL

M1

FO

RA

2834

2824

3826

22K

470R

3853

2813

100R

3864

3867*

220K

2838

10u

+3.3V

2837

47n

HF

VrefCD10

3823

1K

PHOTO DIODES

CD DRIVE on PART1

T

O SER

V

O/MO

T

OR DRIVER

on P

AR

T1

+3.3V

SERIAL DATA

LOOPBACK

INTERFACE

PORE

1.7V 1.7V

3.2V

1.7V

3.2V

3.2V

3.4V

3V

3V

1.6V

1.6V

1.6V

1.6V

1.6V

1.6V

1.6V

1.6V

1.6V

3.2V

0.8V

3.2V

TB = 0.5

µ

s/div

800mVpp

EYE-PATTERN

RW/DA

to part1 7801/pin11

10K

3849

3813

3814

3858*

3861

3717

1R

3759

470R

3716

100R

3712

10R

EB

U

* marked components only forseen

6812

BAS316

A

B

C

D

E

12

13

14

1

2

3

4

5

6

7

8

C

D

E

F

G

H

I

9

10

11

12

13

14

F

G

B

A

1

2

3

4

5

6

7

8

9

10

11

H

I

3.3V

4.1V

. . . V DC voltages measured in

PLAY MODE

with following conditions:

"+10V" = 10V

"+5V" = 5V

EVM

V

2

FE-ST-VK-N

8

7

1

1

FMN-STRK

3

4

3

4

5

6

5

2

9

8

7

6

SHR_STR

EBU

SDA

SILD

GND

SICL

GND

RAB

EBU_GND

Not Connected

Not Connected

SHR_DATA

+10V

CD10_RESET

SW_INFO

SHR_CL

+5V

1805

1802

PORE

SICL

SILD

RAB

EBU

SDA

BC847B

3851

47K

SPEEDSEL

from part3

(7813/7)

6n8

2825

7805

3CDC-LC Herman Mainboard Sheet2 2001-06-29 (CDR Version)

3n3

PORE

SICL

SILD

RAB

EBU

SDA

DOBM

EQSEL

to part1 7804/C

=

DIGITAL AUDIO

1802

C14

1803

G14

1810

B6

2813

A3

2816

D7

2818

C7

2820

G5

2822

A3

2823

B3

2824

B3

2825

A3

2826

D3

2829

G5

2833

B6

2834

B6

2837

B4

2838

A4

2843

C7

2845

C7

3709

A3

3712

G2

3716

F2

3717

G2

3759

F2

3767

E11

3769

F11

3804

F7

3809

B2

3810

G5

3812

F5

3813

F5

3814

F4

3819

G5

3823

A4

3826

B3

3827

B4

3828

B3

3832

G6

3849

F6

3851

A3

3853

A4

3855

D2

3858

G4

3859

G4

3860

G4

3861

G4

3862

B7

3864

A4

3865

D7

3867

A4

6807

F11

6811

G11

6812

B2

7802

A3

7802

C5

7815

F11

0u47

2845

3709

1K

2822

1n8

for double speed only

for quad speed only

+3.3V

3860*

3859*

to CDR Module

for 2x:

2813 = 10n