5-2

5-2

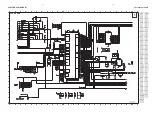

ELECTRICAL DIAGRAM

2

NC

NC

1

VDDSHVREG

VSS

VDDSHV

12

11

10

9

8

7

6

5

4

3

2

1

0

SEL

IN

RST

TICOFF

INH-PG

PG

1

2

TMS

TRST

TDI

TDO

TCK

0

A

CS

DMA

NC

CLK

EMU

D

1

RD

WR

RDY

CS16

ACK

0

1

2

RESET

0

1

DASP

PDIAG

INTRQ

RQ

CF-PF

15

14

13

1

NRZD

SE-PINFLIP

CLOCK

SSM-ERR

DATA

SG

RG-WG

NRZDC

7

6

5

4

3

2

0

NC

NC

NC

NC

NC

NC

NC

GPIO-C

GPIO-E

GPIO-7

GPIO-8

NC

NC

NC

GPIO25

GPIO26

INPUT2

INPUT3

OE2

INPUT4

TDI

TMS

TDO

TCK

GPIO41

GPIO40

GPIO39

GPIO38

GPIO37

GPIO36

GPIO35

GPIO29

GPIO30

GPIO31

GPIO32

GPIO7

GCLR

GPIO6

GPIO5

GPIO4

GPIO3

GPIO2

GPIO1

GCLK2

OE1

GCLK1

GPIO53

GPIO60

GPIO59

GPIO58

GPIO57

GPIO56

GPIO55

GPIO54

VCCINT

GPIO52

GPIO51

GNDIO

GPIO8

GPIO9

GPIO27

GPIO28

VCCIO

NC

GPIO42

GPIO43

GPIO44

GPIO45

GPIO46

GPIO47

GPIO48

GPIO49

GPIO50

GPIO64

GPIO63

GPIO62

GPIO61

GNDINT

INPUT1

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

GPIO18

GPIO19

GPIO20

GPIO21

GPIO22

GPIO23

GPIO24

GPIO34

GPIO33

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

A

B

C

D

E

F

G

H

I

J

K

L

M

N

O

P

Q

A

B

C

D

E

F

G

H

I

J

K

L

M

N

O

P

Q

1013 H20

2005 P 13

2006 P 13

2007 P 13

2008 P 14

2009 P 15

2010 G 19

2011 P 12

2012 M6

2013 M7

2014 M7

2015 M7

2016 M8

2017 M8

2018 M6

2019 M8

2041 J19

2042 J19

2049 P 14

2050 P 14

2051 P 14

2052 P 15

2087 P 15

2093 H10

2094 H10

2097 G 19

2104 F 11

2105 F 10

2108 D22

2109 D22

3025 F 12

3026 E 11

3077-1 I 7

3077-2 I 7

3077-3 I 7

3077-4 I 7

3083 B19

3084 F 12

3093 G 10

3095 G 10

4011-1 K7

4011-2 K7

4011-3 K7

4011-4 K7

4012-1 J7

4012-2 J7

4012-3 J7

4012-4 K7

4013-1 J7

4013-2 J7

4013-3 J7

4013-4 J7

4014-1 K7

4014-2 K7

4014-3 K7

4014-4 K7

4018 J7

4025 C20

5017 G 10

7004 D6

7005-1 M14

7005-2 D14

7005-3 H14

7005-4 J14

7005-5 K14

7010 E 11

7023 F 10

7024 F 11

7027 D19

7028 D20

F201 F 6

F202 G 8

F203 G 8

F204 H6

F205 F 12

F206 H20

F209 H20

F210 H20

F211 H20

F212 H20

F213 H20

F214 H20

F215 H20

F216 H20

F217 H20

F218 I 20

F219 I 20

F220 I 20

F221 I 20

F222 I 20

F223 I 20

F224 I 20

F225 I 20

BC857B

7010

VDCD_E

3026

VDCD_E

10K

VDCD_E

10K

3025

VDCD_E

VDCD_E

VDCD_E

3084

100K

VDCD_E

3077-1

1

8

3

6

3077-2

2

7

3077-4

4

5

3077-3

2097

22u

2105

100n

100n

2104

2094

56p

56p

2093

1K0

3093

1M0

3095

2

3

1

5

4

5

4

7023

74HC1GU04GW

74HC1G14GW

7024

2

3

1

F225

F224

F222

F223

F221

F219

F220

F218

F216

F217

F215

F213

F214

F212

F210

F211

F206

F209

100n

2087

2010

100n

F205

5017

12M

2052

100n

100n

2009

100n

2008

2042

220u

6.3V

220u

2041

6.3V

7

8

9

21

22

15

16

17

18

19

2

20

3

4

5

6

1013

20FLS-RSM1-TB

1

10

11

12

13

14

F203

F202

F204

F201

2019

100n

100n

2018

100n

2017

2016

100n

100n

2015

2014

100n

100n

100n

2013

V3V0_EXT

2012

100n

V3V0_EXT

2011

2051

100n

100n

2050

2049

100n

100n

2007

2006

100n

66

82

100n

2005

24

27

28

49

39

91

3

18

34

51

53

55

70

72

77

78

2

5

7

22

85

6

4

100

87

89

88

90

1

50

71

73

75

76

79

8

80

81

83

84

58

60

61

62

63

9

64

65

67

68

69

42

44

45

46

47

10

48

52

54

56

57

23

21

20

19

12

17

16

15

40

41

92

37

36

35

13

33

32

31

30

29

25

59

74

95

14

99

98

97

96

94

93

38

86

11

26

43

M12

K10

C4

D3

C3

D4

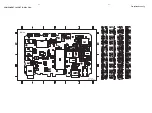

[UNPROG]

PLD

Φ

EPM7064AETC100-10

7004

C6

D10

D11

C9

C10

M4

M3

M7

L9

L10

M11

L11

K3

K11

J3

J11

C11

C5

M6

M5

L8

L7

L6

H3

H11

G11

F2

E11

E3

L5

L4

L3

C7

M8

7005-5

CSS-TIC-000183

DSP

Φ

K13

J12

B12

A13

A12

B11

B2

L2

M2

M9

C2

D2

D1

E2

E1

F1

L12

L13

K12

N3

N4

M1

Φ

GPIO

TEST

CSS-TIC-000183

7005-4

N5

N6

N7

N8

N9

N10

N11

N12

M13

F11

7005-3

CSS-TIC-000183

Φ

SE

REVERSE

SE-PINFLIP="0"

N1

N2

A8

B10

B1

J1

K1

J2

M10

L1

K2

B9

D12

C12

H2

H1

A1

A9

F12

C8

N13

A10

F13

G13

A2

A3

A4

A5

A6

G12

H12

E12

F3

A7

H13

B8

E13

J13

B3

B4

B5

B6

B7

D13

C13

B13

G1

G2

C1

F10

H4

J4

J10

Φ

HOST

CF-PF="0"

REVERSE

CONTROL

JTAG

CLOCK &

CSS-TIC-000183

7005-2

G10

D8

D5

K4

K8

K9

D6

D9

E10

F4

A11

D7

E4

G4

H10

K5

K6

G3

K7

7005-1

CSS-TIC-000183

Φ

SUPPLY

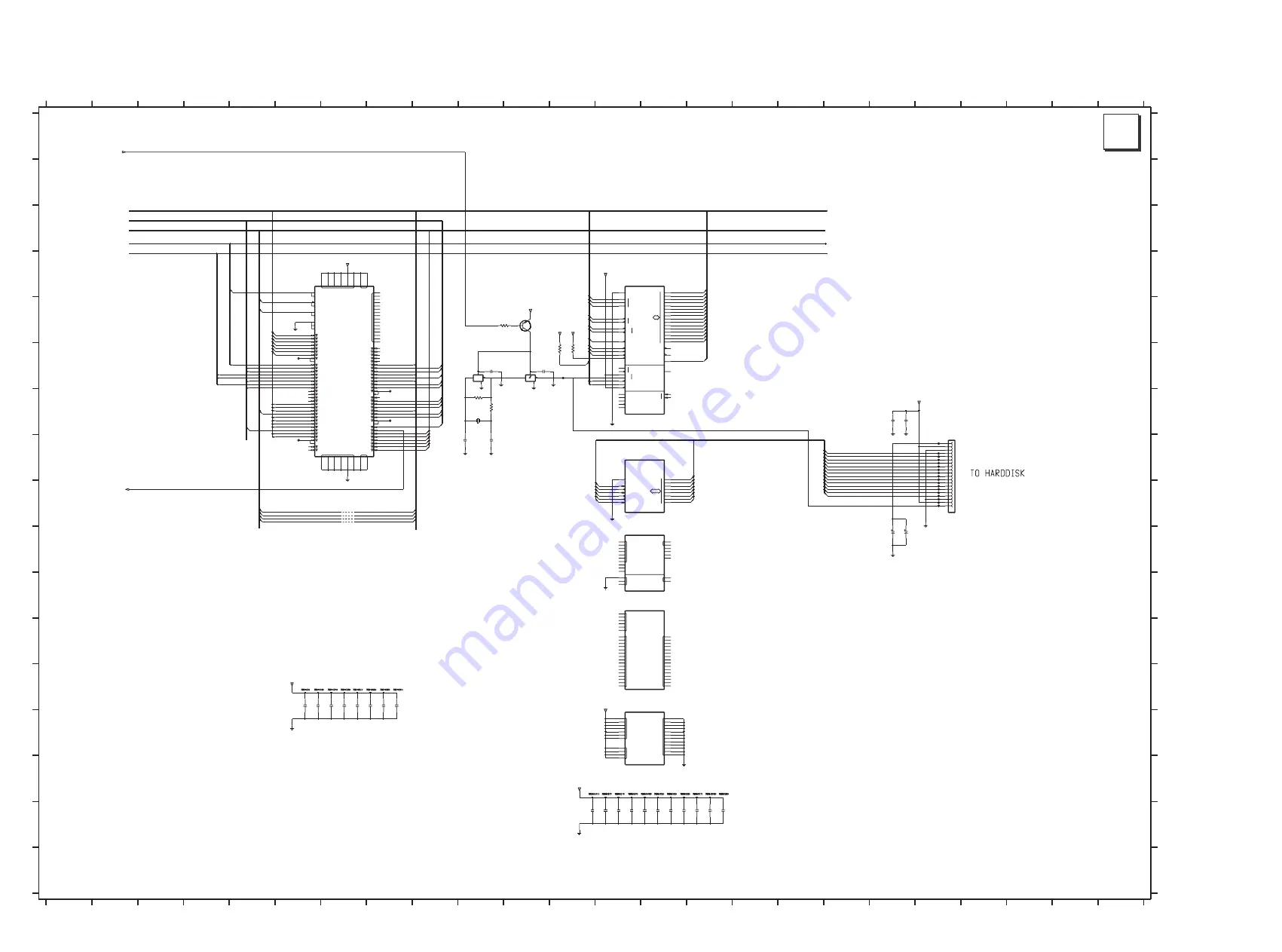

3104 207 5001

bl130-2 dd27-06-03

HD_PWR_CNTR

HD_PWR_CNTR

IORDY_DETECT

IORDY_DETECT

D(6)

D(13)

SD_RAS

{CPLD_OE,CPLD_CS0,CPLD_CS1}

CPLD_OE

CPLD_CS0

CPLD_CS1

IDE_RESET

IDE_TICOFF

IDE_INTRQ

IDE_TICOFF

A(13)

IDE_CS1

IDE_DIOW

IDE_DIOR

IDE_IORDY

D(15)

D(11)

{SD_CLK,SD_CLKE,SD_DQM1,SD_DQM0,SD_RAS,SD_CAS,SD_CS,SD_WE}

SD_CLK

D(14)

D(5)

IDE_DIOR

IDE_DIOW

IDE_IORDY

IDE_DA0

IDE_DA1

IDE_DA2

IDE_CS0

A(10)

A(11)

A(12)

SE_CLOCK

SE_SSM-ERR

IDE_DA0

IDE_DA1

IDE_DA2

IDE_CS0

IDE_CS1

IDE_DMACK

IDE_DMARQ

IDE_RESET

SE_NRZDC

SE_SSM-ERR

SE_DATA

SE_SG

SE_RG-WG

SE_NRZDC

SE_SG

SE_RG-WG

SE_DATA

SE_NRZD(0)

SE_NRZD(1)

SE_NRZD(2)

SE_NRZD(3)

SE_NRZD(4)

SE_NRZD(5)

SE_NRZD(6)

SE_NRZD(7)

SE_CLOCK

IDE_D(15)

A(14)

{SE_NRZD(0:7),SE_NRZDC,SE_SG,SE_RG-WG,SE_DATA,SE_CLOCK,SE_SSM-ERR}

SE_NRZD(0)

SE_NRZD(1)

SE_NRZD(2)

SE_NRZD(3)

SE_NRZD(4)

SE_NRZD(5)

SE_NRZD(6)

SE_NRZD(7)

A(2)

A(1)

A(0)

IDE_D(9)

IDE_D(10)

D(7)

IDE_D(12)

IDE_D(13)

IDE_D(14)

D(1)

IDE_D(4)

IDE_D(8)

IDE_D(11)

A(0:15)

A(7)

A(6)

A(5)

A(4)

A(3)

IDE_D(6)

IDE_D(7)

D(0:15)

D(8)

D(12)

D(9)

D(10)

D(0)

D(4)

D(3)

D(2)

IDE_D(9)

IDE_D(10)

IDE_D(11)

IDE_D(12)

IDE_D(13)

IDE_D(14)

IDE_D(0)

IDE_D(1)

IDE_D(2)

IDE_D(3)

IDE_D(5)

{IDE_D(0:15),IDE_DA0,IDE_DA1,IDE_DA2,IDE_CS0,IDE_CS1,IDE_DMACK,IDE_DMARQ,IDE_RESET,IDE_DIOR,IDE_DIOW,IDE_IORDY,IDE_INTRQ,IDE_TICOFF}

IDE_D(0)

IDE_D(1)

IDE_D(15)

IDE_D(2)

IDE_D(3)

IDE_D(4)

IDE_D(5)

IDE_D(6)

IDE_D(7)

IDE_D(8)

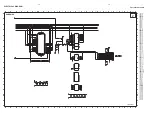

HARDDISK

For reference only