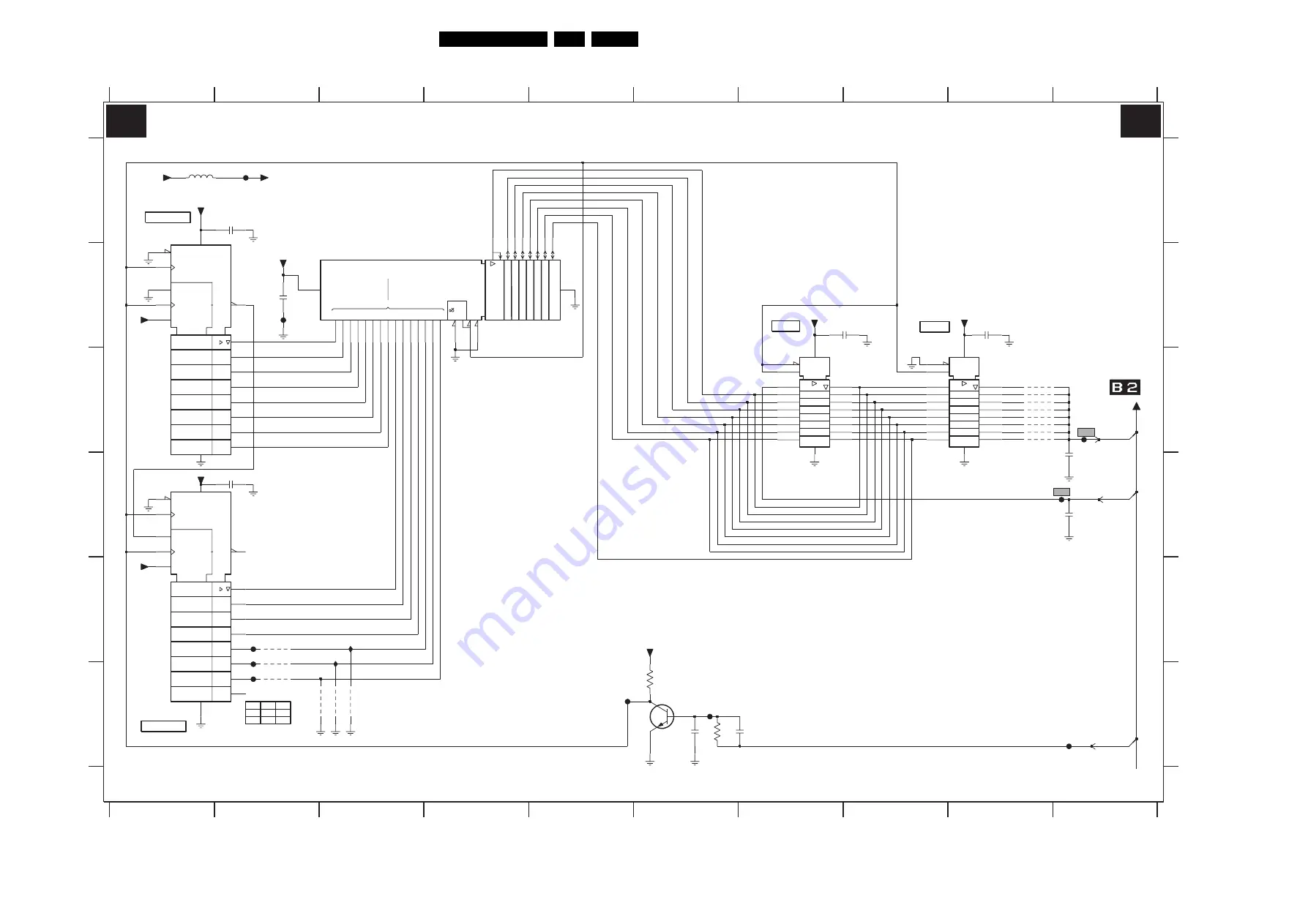

7.

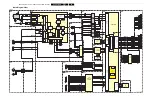

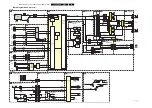

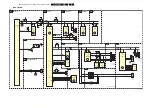

Circuit Diagrams and PWB Layouts

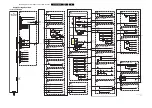

SSB: Audio Delay Line (PDP Only)

EN

C1

1D

EN

C1

1D

2C1

14

13

11

10

9

8

7

6

5

4

3

2

1

0

2EN

32k-1

0

A

A,1D

12

A

G2

C2

G1

1+

CT=0

CTR8

(CT=255)Z4

2D 3

4

EN3

C2

G1

1+

CT=0

CTR8

(CT=255)Z4

2D 3

4

EN3

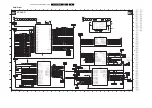

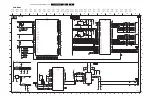

AUDIO DELAY LINE (LIPSYNC) (FOR PDP SETS ONLY)

COUNTER

COUNTER

LATCH

LATCH

2V3

2V3

5V3

5V3

2V6

2V6

2V6

2V6

2V6

2V6

2V6

5V3

2V5

2V5

2V5

2V5

2V5

2V5

2V5

2V5

2V3

5V3

2V3

5V3

5V3

2V6

2V6

2V6

2V6

2V6

2V6

2V6

2V3

0V2

5V3

2V3

2V6

2V3

5V3

2V6

RES

*

RES

RES

RES

RES

RES

RES

RES

RES

*

I505 F2

I506 E3

I507 E3

10

A

B

C

D

E

F

A

B

C

D

E

F

2501 A2

2502 B2

2503 D2

2504 B8

2505 B9

2506 C10

2507 D10

2508 F6

2509 F7

3501 F6

3502 F6

4501 E2

4502 F2

4503 F2

4504 F2

4505 F3

4506 F3

I505

1

2

3

4

5

6

7

8

9

10

1

2

3

4

5

6

7

8

9

4507 C9

4508 C9

4509 C9

4510 C9

4511 C9

4512 C9

4513 C9

4514 C9

5501 A1

7501 A1

7502 B3

7503 F1

7504 F6

7505 B7

7506 B8

F501 A2

F502 B2

F503 C10

F504 D10

F505 F10

I501 F5

I502 F6

I503 E2

I504 E2

I506

I507

I504

I503

22

28

27

F502

5

20

11

12

13

15

16

17

18

19

14

8

9

10

24

25

26

1

2

3

4

RAM

32kx8

7502

CY62256LL-70ZC

21

23

6

7

2508

82p

2507

470p

20

2506

330p

11

1

19

18

17

16

15

14

13

12

2

3

4

5

6

7

8

9

10

13

12

20

7505

74HC573PW

10

11

1

19

18

17

16

15

14

2

3

4

5

6

7

8

9

F505

7506

74HC573PW

4506

4504

I501

I502

F503

F504

4513

4514

4512

4510

4511

4509

4508

+5VD

4507

4501

4505

4503

4502

BC847BW

47K

3502

7504

470R

3501

82p

2509

+5VD

100n

2505

+5VD

100n

2504

+5VD

+5VD

100n

2502

+5VD

100n

2503

+5VD

2501

100n

+5VD

+5VD

F501

1u0

5501

5

6

7

13

9

16

VCC

+5VSWI

8

GND

14

15

1

2

3

4

M74HC590T

7503

11

12

10

5

6

7

13

9

VCC

16

8

GND

14

15

1

2

3

4

M74HC590T

7501

11

12

10

I2SDI1

I2SCLK

I2SDO1

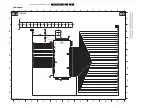

G_16210_004.eps

160106

3139 123 6117.2

B4

B4

4503

4504

LCD PDP

N

Y

Y

N

*