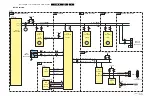

Circuit Diagrams and PWB Layouts

37

7.

SSB: DDR Flash Trap

VCC

Q

VSS

D

C

S

W

HOLD

5

6

1

2

3

CLK

DM

U

L

VREF

10

CLK

VSS

9

14

13

VSSQ

2

CAS

WE

15

RAS

0

CKE

6

12

8

1

0

VDDQ

D

A

DQS

L

U

VDD

7

1

0

NC

10

11

NC

3

7

8

9

11

4

12

4

BA

CS

5

1701 B9

2701 B2

8

1

2

3

4

5

6

F

DDR FLASH TRAP

2702 B3

2703 B3

2704 B3

2705 D2

2706 D2

2707 F3

2709 B4

2710 B4

2711 B5

2712 B5

3703 D2

3706 F3

3708 A7

3709 A8

F709 C8

F710 C8

F711 D3

F712 D8

I701 F3

2714 E8

3722 E6

3723 E7

3724 E8

3710 A8

3711 A8

3712 A9

3713 A9

3714 B9

3715 B9

4

5

6

7

HY5DU281622FTP-5

3716 B9

3717 C9

3718 C9

3719 C9

3720 E6

3721 E6

F

A

B

C

D

E

2713 B5

3701 C2

3702 D2

5701 D8

7701 B3

7702 E7

F701 F6

F702 E7

F703 E9

7

8

9

1

2

3

3

9

F704 F6

F705 B7

F706 E7

F707 F6

F708 C8

A

B

C

D

E

6

5

7

2

1

8

4

7702

M25P80-VMW6T

FLASH

8M

Φ

5701

600R

10u

2701

+3V3_SW

2709

I701

F705

470n

F709

F708

F710

F707

3706

220R

1n0

2707

3719

2K2

470n

2711

+2V5_SW

F701

3724

33R

F703

3721

47K

+2V5_SW

47K

3722

2K2

3717

1701

319804000020

1

2

3711

10K

3712

47K

33R

3723

470n

2714

47K

3720

+3V3_SW

2706

470n

3714

10K

470n

2705

+2V5_SW

2704

470n

F712

58

64

21

15

55

61

49

34

48

66

6

12

52

50

53

23

47

51

1

18

33

3

9

13

54

56

20

16

14

17

19

25

43

57

59

60

62

63

65

5

7

8

10

11

40

26

27

22

44

45

46

24

2

4

30

28

41

42

31

32

35

36

37

38

39

7701

SDRAM

2Mx16x4

Φ

29

2702

470n

DDR

F702

F704

10K

3710

3709

47K

47K

3708

1K0

3716

47K

3713

10K

3718

4K7

3715

4K7

3701

4K7

3703

1%

2713

470n

470n

2703

F711

1%

4K7

3702

470n

2712

F706

MD(2)

2710

470n

MD(9)

MA(1)

MD(6)

MA(8)

MA(6)

MD(5)

MA(5)

MD(0)

MA(9)

MA(10)

DQM0L

CASN

DQM0H

MA(3)

MA(0)

MA(2)

MD(13)

MD(12)

CKE

RASN

MD(10)

MD(8)

MD(3)

WEN

MD(4)

MA(7)

DQS0H

MA(4)

BA1

MD(1)

MD(11)

BA0

HPD_RST_MUX

DQS0L

MA(11)

MD(7)

MD(14)

CKE

SPI_CEN

SPI_SCK

TRAP4

SPI_HOLD

SPI_SDI

TRAP2

SPI_SCK

SPI_CEN

SPI_SDO

SDCLKN

SDCLKN

SDCLKP

SDCLKP

MD(15)

B04B

B04B

I_18170_005.eps

170708

3139 123 6425.1