1998 Feb 16

11

Philips Semiconductors

Product specification

CMOS digital decoding IC with RAM for

Compact Disc

SAA7345

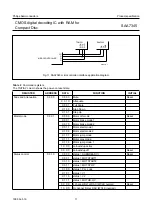

Table 2 Command registers.

The ‘INITIAL’ column shows the power-on reset state

REGISTER

ADDRESS

DATA

FUNCTION

INITIAL

Fade and Attenuation

0 0 0 0

X 0 0 0

Mute

Reset

X 0 1 X

Attenuate

X 0 0 1

Full Scale

X 1 0 0

Step Down

X 1 0 1

Step Up

Motor mode

0 0 0 1

X 0 0 0

Motor off mode

Reset

X 0 0 1

Motor brake mode 1

X 0 1 0

Motor brake mode 2

X 0 1 1

Motor start mode 1

X 1 0 0

Motor start mode 2

X 1 0 1

Motor jump mode

X 1 1 1

Motor play mode

X 1 1 0

Motor jump mode 1

1 X X X

anti-windup active

0 X X X

anti-windup off

Reset

Status control

0 0 1 0

X 0 0 0

status = SUBQREADY-I

Reset

X 0 0 1

status = MOTSTART1

X 0 1 0

status = MOTSTART2

X 0 1 1

status = MOTSTOP

X 1 0 0

status = PLL Lock

X 1 0 1

status = V1

X 1 1 0

status = V2

X 1 1 1

status = MOTOR-OV

0 X X X

L channel first at DAC (WCLK normal)

Reset

1 X X X

R channel first at DAC (WCLK inverted)

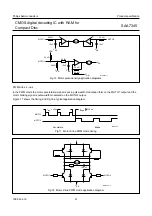

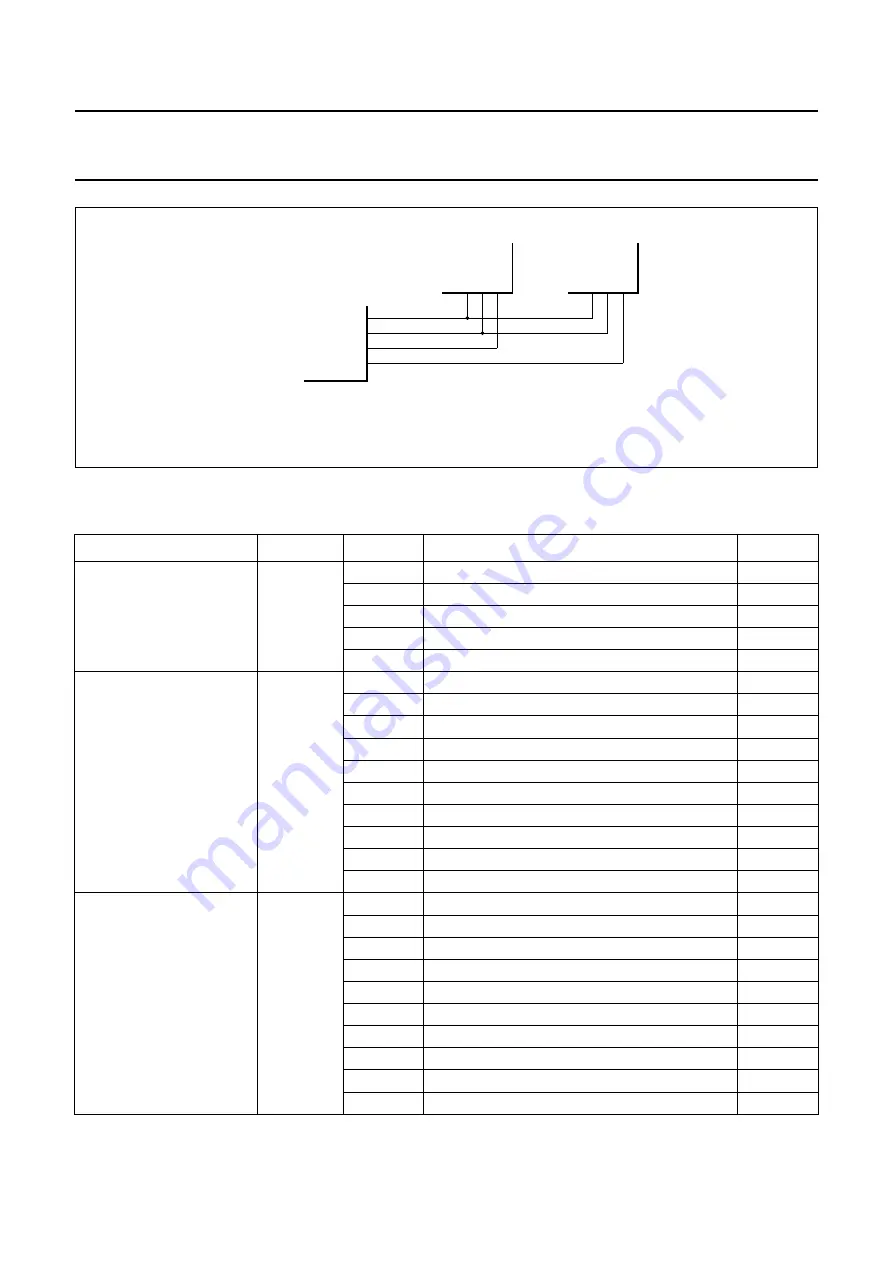

Fig.11 SAA7345 microcontroller interface application diagram.

MGA361 - 1

MICROCONTROLLER

TDA1301

SAA7345

I/O

O

O

O

SIDA

SICL

SILD

DA

CL

RAB