1998 Feb 16

12

Philips Semiconductors

Product specification

CMOS digital decoding IC with RAM for

Compact Disc

SAA7345

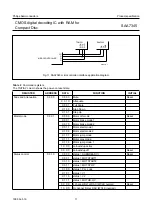

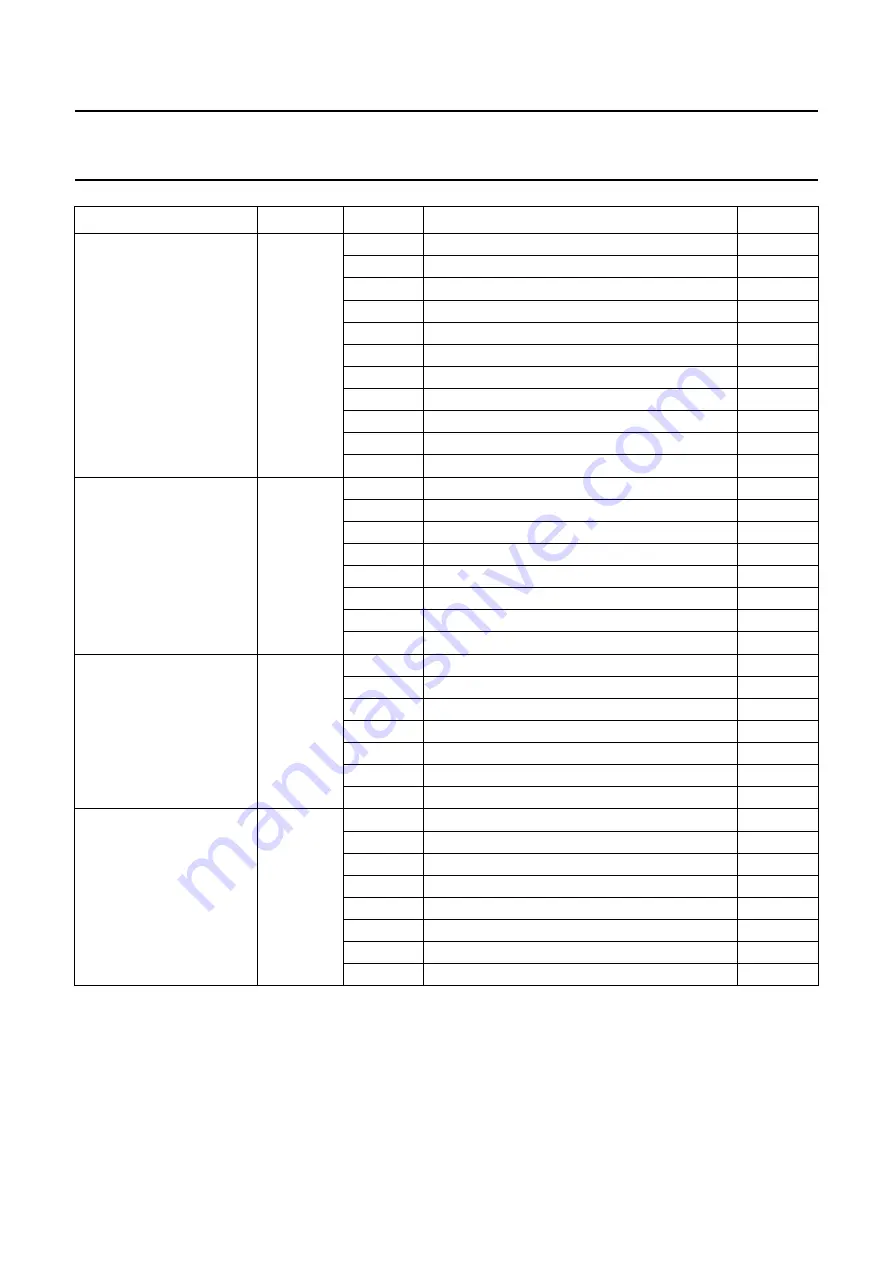

DAC output

0 0 1 1

1 0 1 0

I

2

S CD-ROM mode

1 0 1 1

EIAJ; CD-ROM mode

1 1 0 X

I

2

S; 4f

s

mode

Reset

1 1 1 1

I

2

S; 2f

s

mode

1 1 1 0

I

2

S; f

s

mode

0 0 0 X

EIAJ; 16-bit; 4f

s

0 0 1 1

EIAJ; 16-bit; 2f

s

0 0 1 0

EIAJ; 16-bit; f

s

0 1 0 X

EIAJ; 18-bit; 4f

s

0 1 1 1

EIAJ; 18-bit; 2f

s

0 1 1 0

EIAJ; 18-bit; f

s

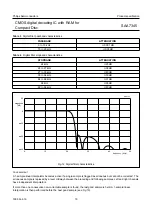

Motor gain

0 1 0 0

X 0 0 0

Motor gain G = 3.2

Reset

X 0 0 1

Motor gain G = 4.0

X 0 1 0

Motor gain G = 6.4

X 0 1 1

Motor gain G = 8.0

X 1 0 0

Motor gain G = 12.8

X 1 0 1

Motor gain G = 16.0

X 1 1 0

Motor gain G = 25.6

X 1 1 1

Motor gain G = 32.0

Motor bandwidth

0 1 0 1

X X 0 0

Motor f

4

= 0.5 Hz

Reset

X X 0 1

Motor f

4

= 0.7 Hz

X X 1 0

Motor f

4

= 1.4 Hz

X X 1 1

Motor f

4

= 2.8 Hz

0 0 X X

Motor f

3

= 0.85 Hz

Reset

0 1 X X

Motor f

3

= 1.71 Hz

1 0 X X

Motor f

3

= 3.42 Hz

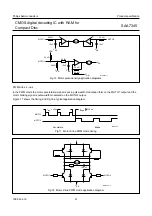

Motor output configuration

0 1 1 0

X X 0 0

Motor power maximum 37%

Reset

X X 0 1

Motor power maximum 50%

X X 1 0

Motor power maximum 75%

X X 1 1

Motor power maximum 100%

0 0 X X

MOTO1, MOTO2 pins 3-state

Reset

0 1 X X

Motor Pulse Width Modulation (PWM) mode

1 0 X X

Motor Pulse Density Modulation (PDM) mode

1 1 X X

Motor Compact Disc Video (CDV) mode

REGISTER

ADDRESS

DATA

FUNCTION

INITIAL