1998 Feb 16

13

Philips Semiconductors

Product specification

CMOS digital decoding IC with RAM for

Compact Disc

SAA7345

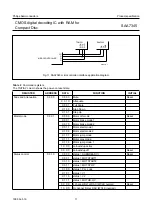

Loop BW

(Hz)

Internal BW

(Hz)

Low-pass

BW (Hz)

PLL loop filter bandwidth

1 0 0 0

0 0 0 0

1640

525

8400

0 0 0 1

3279

263

16800

0 0 1 0

6560

131

33600

0 1 0 0

1640

1050

8400

0 1 0 1

3279

525

16800

0 1 1 0

6560

263

33600

1 0 0 0

1640

2101

8400

1 0 0 1

3279

1050

16800

Reset

1 0 1 0

6560

525

33600

1 1 0 0

1640

4200

8400

1 1 0 1

3279

2101

16800

1 1 1 0

6560

1050

33600

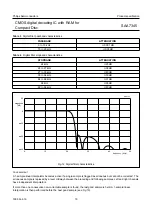

PLL loop filter equalization

1 0 0 1

0 0 0 1

PLL 30 ns over-equalization

0 0 1 0

PLL 15 ns over-equalization

0 0 1 1

PLL nominal equalization

Reset

0 1 0 0

PLL 15 ns under-equalization

0 1 0 1

PLL 30 ns under-equalization

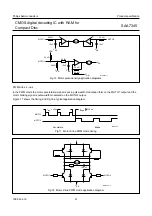

EBU output

1 0 1 0

X X 0 0

EBU data before concealment

X X 1 0

EBU data after concealment and fade

Reset

X X 1 1

EBU off

−

output LOW

X 0 X X

Level II clock accuracy (

<

1000

×

10

−

6

)

Reset

X 1 X X

Level III clock accuracy (

>

1000

×

10

−

6

)

0 X X X

Flags in EBU off

Reset

1 X X X

Flags in EBU on

Speed control

1 0 1 1

1 X X X

double-speed mode

0 X X X

single-speed mode

Reset

X 0 X X

33.869 MHz crystal present

Reset

X 1 X X

16.934 MHz crystal present

X X 0 0

standby 1: ‘CD-STOP’ mode (note 1)

Reset

X X 1 0

standby 2: ‘CD-PAUSE’ mode (note 1)

X X 1 1

operating mode

Versatile pins interface

1 1 0 0

X X X 1

off-track input at V1

X X X 0

no off-track input (V1 may be read via status)

Reset

X X 0 X

Kill-L at KILL output, Kill-R at V3 output

X 0 1 X

V3 = 0; single Kill output

Reset

X 1 1 X

V3 = 1; single Kill output

REGISTER

ADDRESS

DATA

FUNCTION

INITIAL