Philips Semiconductors

SC16C2550

Dual UART with 16 bytes of transmit and receive FIFOs and IrDA

encoder/decoder

Product data

Rev. 03 — 19 June 2003

10 of 46

9397 750 11621

© Koninklijke Philips Electronics N.V. 2003. All rights reserved.

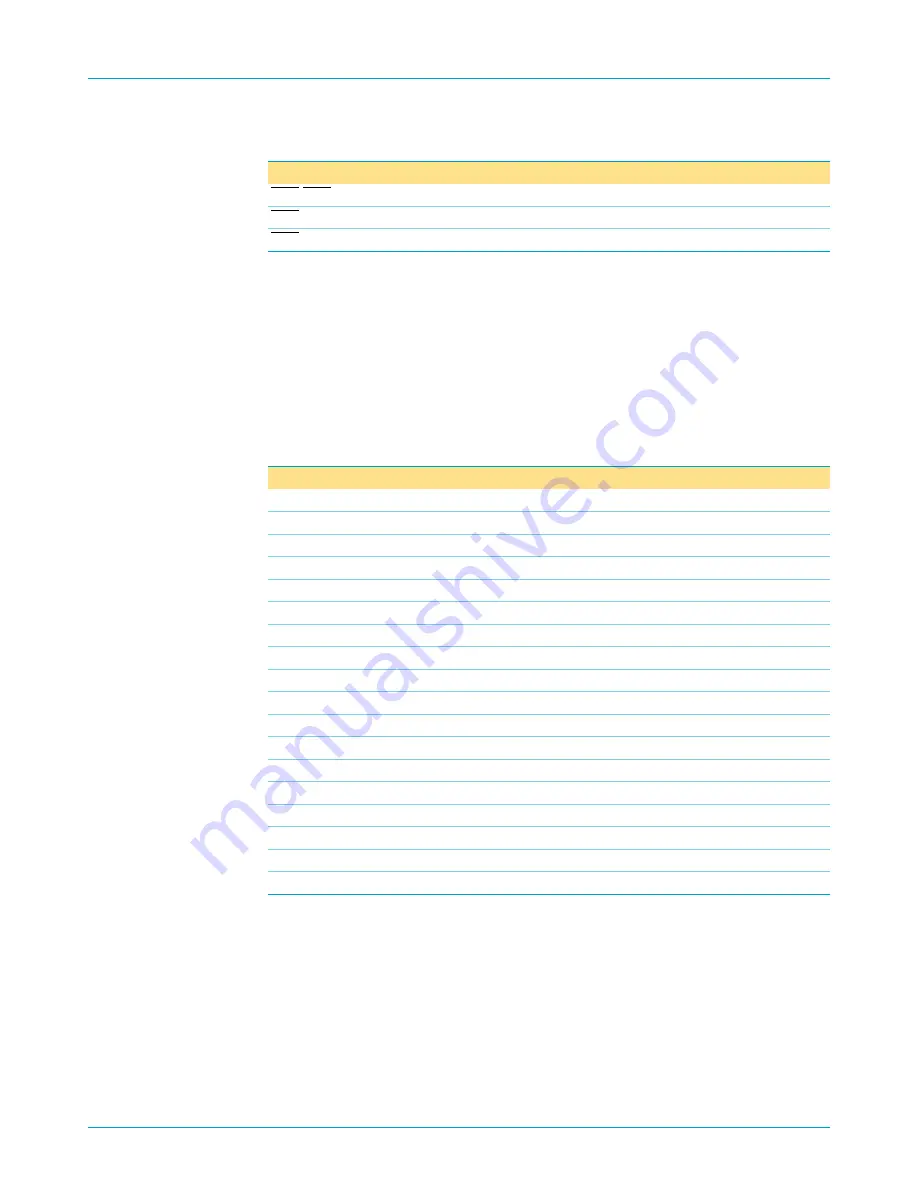

6.2 Internal registers

The SC16C2550 provides two sets of internal registers (A and B) consisting of

12 registers each for monitoring and controlling the functions of each channel of the

UART. These registers are shown in

. The UART registers function as data

holding registers (THR/RHR), interrupt status and control registers (IER/ISR), a FIFO

control register (FCR), line status and control registers (LCR/LSR), modem status

and control registers (MCR/MSR), programmable data rate (clock) control registers

(DLL/DLM), and a user accessible scratchpad register (SPR).

[1]

These registers are accessible only when LCR[7] is a logic 0.

[2]

These registers are accessible only when LCR[7] is a logic 1.

[3]

Enhanced Feature Register, Xon1, 2 and Xoff1, 2 are accessible only when the LCR is set to

‘BF(HEX)’.

Table 3:

Serial port selection

Chip Select

Function

CSA-CSB = 1

none

CSA = 0

UART channel A

CSB = 0

UART channel B

Table 4:

Internal registers decoding

A2

A1

A0

READ mode

WRITE mode

General register set (THR/RHR, IER/ISR, MCR/MSR, FCR, LSR, SPR)

0

0

0

Receive Holding Register

Transmit Holding Register

0

0

1

Interrupt Enable Register

0

1

0

Interrupt Status Register

FIFO Control Register

0

1

1

Line Control Register

1

0

0

Modem Control Register

1

0

1

Line Status Register

n/a

1

1

0

Modem Status Register

n/a

1

1

1

Scratchpad Register

Scratchpad Register

Baud rate register set (DLL/DLM)

0

0

0

LSB of Divisor Latch

LSB of Divisor Latch

0

0

1

MSB of Divisor Latch

MSB of Divisor Latch

Enhanced register set (EFR, Xon/off 1-2)

0

1

0

Enhanced Feature Register

Enhanced Feature Register

1

0

0

Xon1 word

Xon1 word

1

0

1

Xon2 word

Xon2 word

1

1

0

Xoff1 word

Xoff1 word

1

1

1

Xoff2 word

Xoff2 word