Circuit Descriptions, Abbreviation List, and IC Data Sheets

EN 39

SK5.1L CA

9.

9.4.6

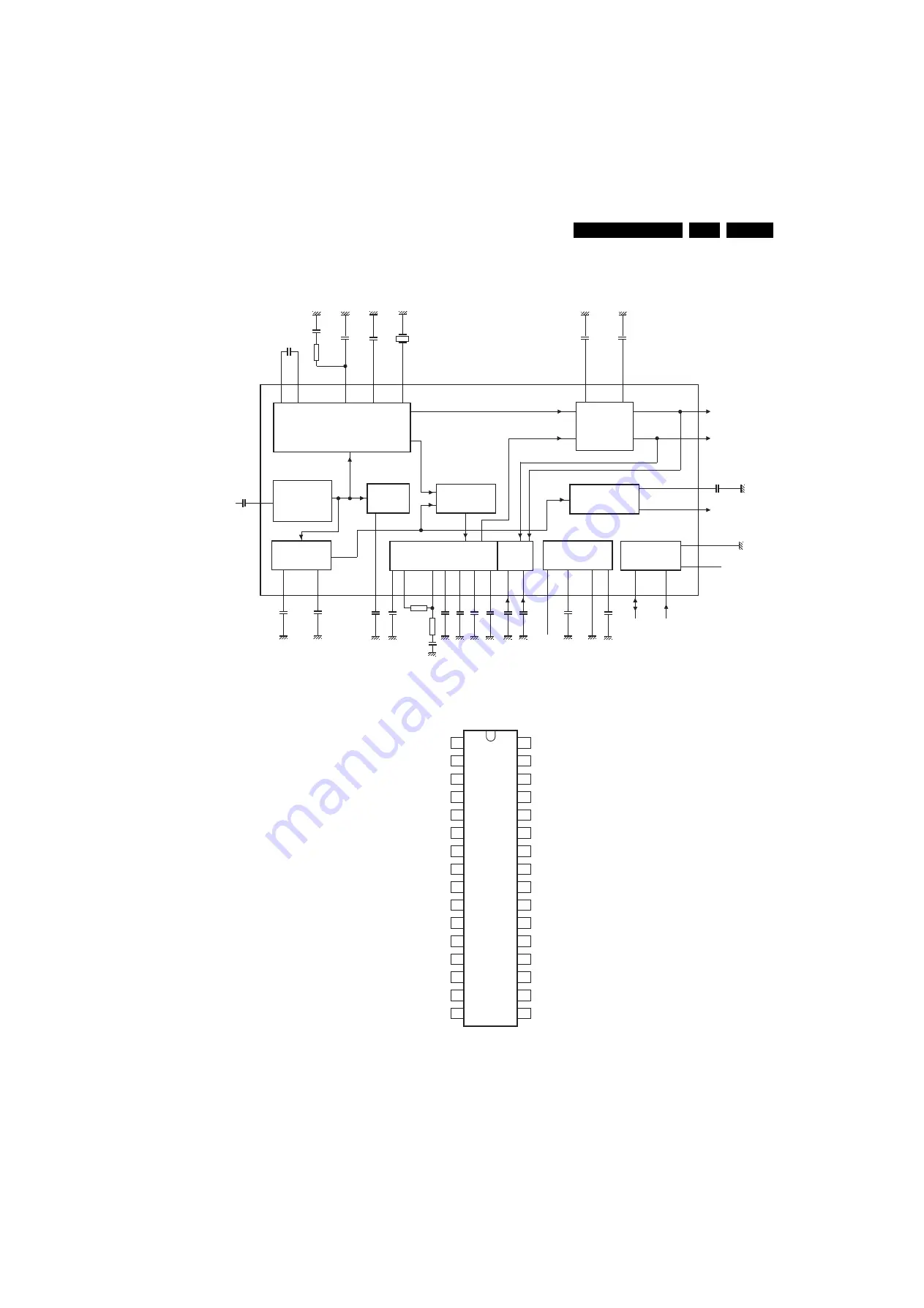

Diagram A6, TDA9850, (IC740)

Figure 9-7 Block Diagram and Pin Configuration

compo

s

ite

bas

e

ba

nd

inp

u

t

+

+

C2

1

3

14

15

C5

16

Q1

cer

a

mic

re

s

on

a

tor

17

DEMATRIX

+

MODE

S

ELECT

+

C6

1

8

+

C7

19

DE-EMPHA

S

I

S

L + R

L

−

R/

S

AP

OUTL

OUTR

27

21

S

TEREO DECODER

S

AP witho

u

t DBX

2

3

C

8

22

R1

C

3

C4

LOGIC, I

2

C-

TRAN

S

CEIVER

MAD

2

8

7

s

tereo

mono

S

AP

to

au

dio

proce

ss

ing

9

8

S

DA

S

CL

S

UPPLY

+

C1

8

24

6

+

C19

12

10

V

ref

V

CAP

V

CC

S

AP

DEMODULATOR

+

C16

5

C15

4

INPUT

LEVEL

ADJU

S

T

+

11

C1

NOI

S

E

DETECTOR

S

TEREO/

S

AP

S

WITCH

C17

26

TDA9

8

50

S

TEREO

ADJU

S

T

DBX

+

C14

3

C1

3

R

3

R2

1

2

+

3

2

+

3

1

+

3

0

+

29

C12 C11 C10 C9

+

25

+

20

C

L

C

R

only d

u

ring

a

dj

us

tment

TDA9

8

50

1

2

3

4

5

6

7

8

9

10

11

12

1

3

14

15

16

3

2

3

1

3

0

29

2

8

27

26

25

24

2

3

22

21

20

19

1

8

17

VEO

C

S

CW

CT

S

CTW

CND

C

S

DE

CL

CR

C

SS

CMO

Vref

VEI

CNR

CM

CDEC

L

T

U

O

D

N

G

A

S

AP

OUTR

CER

MAD

DGND

S

DA

S

CL

VCC

COMP

VCAP

CP1

CP2

CPH

CADJ

Block Dia

g

ram

Pin Confi

g

uration

H_17450_004.ep

s

200907